# **PIC12C67X**

## PIC12C67X Rev. A Silicon Errata Sheet

The PIC12C67X (Rev. A) parts you have received conform functionally to the Device Data Sheet (**DS30561**), except for the anomalies described below.

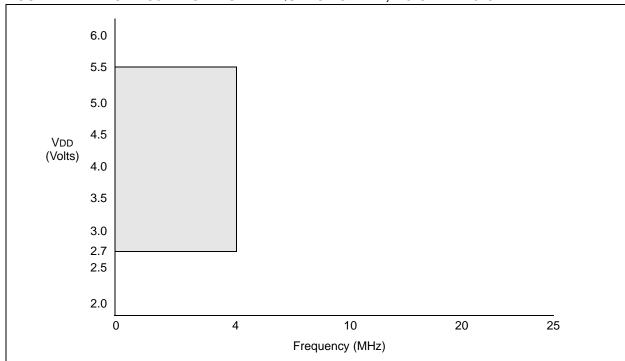

FIGURE 1: PIC12LC67X VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}$ C  $\leq$  Ta  $\leq$  0 $^{\circ}$ C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

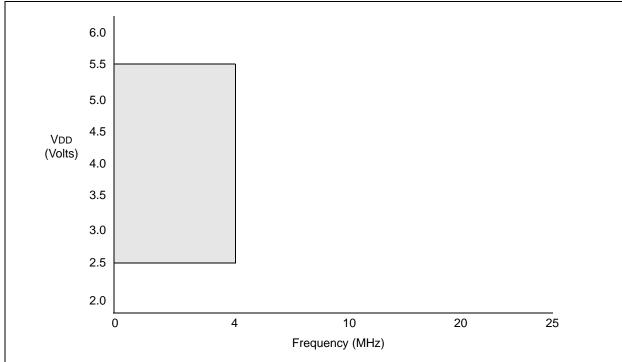

FIGURE 2: PIC12LC67X VOLTAGE-FREQUENCY GRAPH, 0°C ≤ TA ≤ +70°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

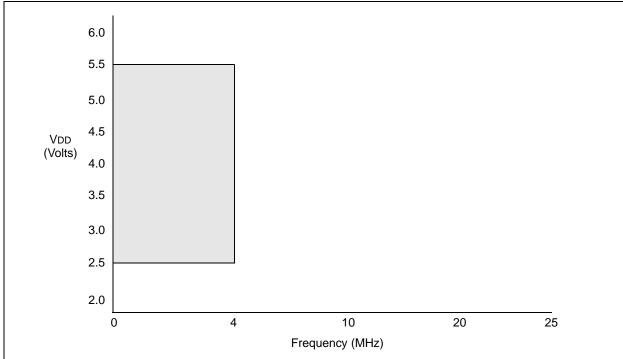

FIGURE 3: PIC12LC67X VOLTAGE-FREQUENCY GRAPH, +70°C ≤ Ta ≤ +85°C

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

#### Clarifications/Corrections to the Data Sheet:

In the Device Data Sheet (**DS30561B**), the following clarifications and corrections should be noted.

In Section 4.0, corrections for the Special Function Register Summary, Table 4-1, are shown. Correction for the "OSCCAL" Register, Section 4.2.2.7, is shown. Clarification to the "GPIO", Section 5.1 is provided. Corrections for the Internal 4 MHz RC Oscillator, Section 9.2.5, are shown. Corrections for Section 9.0, Initialization Conditions for all registers, Table 9-7, are shown. Corrections for the DC Characteristics, Sections 12.3 and 12.4 are shown.

Corrections for the GPIO pull-up resistor ranges are shown in Table 12-6.

TABLE 4-1: PIC12C67X SPECIAL FUNCTION REGISTER SUMMARY

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets <sup>(3)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------------------------|

| Bank 1  |        |       |       |       |       |       |       |       |       |                               |                                                |

| 8Fh     | OSCCAL | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | _     | _     | 1000 00                       | uuuu uu                                        |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved on the PIC12C67X; always maintain these bits clear.

- 5: The SCL (GP7) and SDA (GP6) bits are unimplemented on the PIC12C671/672 and read as '0'.

#### 4.2.2.7 OSCCAL REGISTER

The Oscillator Calibration (OSCCAL) Register is used to calibrate the internal 4 MHz oscillator. It contains six bits for calibration. Increasing the calue value increases the frequency.

#### REGISTER 4-7: OSCCAL REGISTER (ADDRESS 8Fh)

| R/W-1    | R/W-0                         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0  |                                       |  |

|----------|-------------------------------|-------|-------|-------|-------|-----|------|---------------------------------------|--|

| CAL5     | CAL4                          | CAL3  | CAL2  | CAL1  | CAL0  | _   | _    | R = Readable bit                      |  |

| bit7     |                               |       |       |       |       |     | bit0 | W = Writable bit                      |  |

|          |                               |       |       |       |       |     |      | U = Unimplemented bit,<br>read as '0' |  |

|          |                               |       |       |       |       |     |      | - n = Value at POR reset              |  |

| bit 7-2: | : CAL<5:0>: Calibration       |       |       |       |       |     |      |                                       |  |

| bit 1-0: | ): Unimplemented: Read as '0' |       |       |       |       |     |      |                                       |  |

|          | -                             |       |       |       |       |     |      |                                       |  |

## PIC12C67X

#### **5.1 GPIO**

GPIO is an 8-bit I/O register. Only the low order 6 bits are used (GP<5:0>). Bits 6 and 7 (SDA and SCL, respectively) are used by the EEPROM peripheral on the PIC12CE673/674. Refer to Section 6.0 and Appendix B for use of SDA and SCL. Please note that GP3 is an input only pin. The configuration word can set several I/O's to alternate functions. When acting as alternate functions, the pins will read as '0' during port read.

Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also with interrupt-on-change. The interrupt on change and weak pull-up functions are <u>not</u> pin selectable. If pin 4, (GP3), is configured as MCLR, a weak pull-up is always on. Interrupt-on-change for this pin is not set and GP3 will read as '0'. Interrupt-on-change is enabled by setting bit GPIE, INTCON<3>.

The interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of GPIO will end the mismatch condition.

- b) Clear flag bit GPIF.

A mismatch condition will continue to set flag bit GPIF. Reading GPIO will end the mismatch condition and allow flag bit GPIF to be cleared.

Note that external oscillator use overrides the GPIO functions on GP4 and GP5.

#### 9.2.5 INTERNAL 4 MHz RC OSCILLATOR

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency. Only bits<7:2> of OSCCAL are implemented, and bits<1:0> should be written as 0 for compatibility with future devices. The oscillator calibration location is not code protected.

TABLE 9-7: INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register Power-on Reset |         | MCLR Resets<br>WDT Reset | Wake-up via<br>WDT or Interrupt |  |  |

|-------------------------|---------|--------------------------|---------------------------------|--|--|

| OSCCAL                  | 1000 00 | uuuu uu                  | uuuu uu                         |  |  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition.

Note 1: One or more bits in INTCON and PIR1 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 9-5 for reset value for specific condition.

- 4: If wake-up was due to A/D completing then bit 6 = 1, all other interrupts generating a wake-up will cause bit 6 = u.

- 5: If wake-up was due to A/D completing then bit 3 = 0, all other interrupts generating a wake-up will cause bit 3 = u.

Engineering Samples for the PIC12C671/2 may or may not follow this operational clarification for the OSCCAL register.

DC CHARACTERISTICS

## 12.3 DC CHARACTERISTICS: PIC12C671/672 (Commercial, Industrial, Extended) PIC12CE673/674 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise specified)

Operating temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  (commercial)

$-40^{\circ}$ C  $\leq$  TA  $\leq$  +85 $^{\circ}$ C (industrial) -40 $^{\circ}$ C  $\leq$  TA  $\leq$  +125 $^{\circ}$ C (extended)

Operating voltage VDD range as described in DC spec Section 12.1 and

Section 12.2.

| Param | Characteristic                     | Sym  | Min | Typ† | Max        | Units | Conditions             |  |  |

|-------|------------------------------------|------|-----|------|------------|-------|------------------------|--|--|

| No.   |                                    |      |     |      |            |       |                        |  |  |

|       | Input Leakage Current (Notes 2, 3) |      |     |      |            |       |                        |  |  |

|       |                                    | lı∟  |     |      |            |       |                        |  |  |

| D061  | GP3/MCLR (Note 5)                  |      | 8   | 130  | 250        | μΑ    | $Vss \le Vpin \le Vdd$ |  |  |

| D061A | GP3/MCLR (Note 6)                  |      |     |      | <u>+</u> 5 | μΑ    | $Vss \le Vpin \le Vdd$ |  |  |

| D070  | GPIO weak pull-up current (Note 4) | IPUR | 50  | 250  | 400        | μΑ    | VDD = 5V, VPIN = VSS   |  |  |

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin.

- 4: Does not include GP3. For GP3 see parameters D061 and D061A.

- 5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

- 6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

## 12.4 DC CHARACTERISTICS: PIC12LC671/672 (Commercial, Industrial) PIC12LCE673/674 (Commercial, Industrial)

| DC CHA       | RACTERISTICS                       | Standard Operating Conditions (unless otherwise specified)  Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial) $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial)  Operating voltage VDD range as described in DC spec Section 12.1 and Section 12.2. |     |      |            |       |                      |  |

|--------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------------|-------|----------------------|--|

| Param<br>No. |                                    |                                                                                                                                                                                                                                                                             | Min | Тур† | Max        | Units | Conditions           |  |

|              | Input Leakage Current (Notes 2, 3) |                                                                                                                                                                                                                                                                             |     |      |            |       |                      |  |

|              |                                    | II∟                                                                                                                                                                                                                                                                         |     |      |            |       |                      |  |

| D061         | GP3/MCLR (Note 5)                  |                                                                                                                                                                                                                                                                             | 8   | 130  | 250        | μΑ    | Vss ≤ Vpin ≤ Vdd     |  |

| D061A        | GP3/MCLR (Note 6)                  |                                                                                                                                                                                                                                                                             |     |      | <u>+</u> 5 | μΑ    | Vss ≤ Vpin ≤ Vdd     |  |

| D070         | GPIO weak pull-up current (Note 4) | Ipur                                                                                                                                                                                                                                                                        | 50  | 250  | 400        | μΑ    | VDD = 5V, VPIN = VSS |  |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC12C67X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin.

- **4:** Does not include GP3. For GP3 see parameters D061 and D061A.

- 5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

- 6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

TABLE 12-6: GPIO PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min  | Тур              | Max   | Units |  |  |  |  |  |  |

|-------------|------------------|------|------------------|-------|-------|--|--|--|--|--|--|

|             | GP0/GP1          |      |                  |       |       |  |  |  |  |  |  |

| 2.5         | -40              | 38K  | 42K              | 63K   | Ω     |  |  |  |  |  |  |

|             | 25               | 42K  | 48K              | 63K   | Ω     |  |  |  |  |  |  |

|             | 85               | 42K  | 49K              | 63K   | Ω     |  |  |  |  |  |  |

|             | 125              | 50K  | 55K              | 63K   | Ω     |  |  |  |  |  |  |

| 5.5         | -40              | 15K  | 17K              | 20K   | Ω     |  |  |  |  |  |  |

|             | 25               | 18K  | 20K              | 23K   | Ω     |  |  |  |  |  |  |

|             | 85               | 19K  | 22K              | 25K   | Ω     |  |  |  |  |  |  |

|             | 125              | 22K  | 24K              | 28K   | Ω     |  |  |  |  |  |  |

|             |                  | GP   | 3 <sup>(1)</sup> |       |       |  |  |  |  |  |  |

| 2.5         | -40              | 65K  | 80K              | 850K  | Ω     |  |  |  |  |  |  |

|             | 25               | 80K  | 100K             | 1150K | Ω     |  |  |  |  |  |  |

|             | 85               | 85K  | 110K             | 1300K | Ω     |  |  |  |  |  |  |

|             | 125              | 100K | 120K             | 1500K | Ω     |  |  |  |  |  |  |

| 5.5         | -40              | 50K  | 60K              | 600K  | Ω     |  |  |  |  |  |  |

|             | 25               | 60K  | 65K              | 750K  | Ω     |  |  |  |  |  |  |

|             | 85               | 65K  | 80K              | 900K  | Ω     |  |  |  |  |  |  |

|             | 125              | 75K  | 90K              | 990K  | Ω     |  |  |  |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** The weak pull-up resistor and associated current for the GP3/MCLR pin is non-linear when the respective pin voltage is less than VDD - 1.0V. See parameter D061 for GP3/MCLR pin current specifications.

### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

#### **Corporate Office**

Microchip Technology Inc. 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-786-7200 Fax: 480-786-7277 Technical Support: 480-786-7627 Web Address: http://www.microchip.com

#### Atlanta

Microchip Technology Inc. 500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### **Boston**

Microchip Technology Inc. 2 LAN Drive, Suite 120 Westford, MA 01886 Tel: 508-480-9990 Fax: 508-480-8575

#### Chicago

Microchip Technology Inc. 333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

#### **Dallas**

Microchip Technology Inc. 4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

#### Dayton

Microchip Technology Inc. Two Prestige Place, Suite 150 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

#### Detroit

Microchip Technology Inc. Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

#### Los Angeles

Microchip Technology Inc. 18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

### **New York**

Microchip Technology Inc. 150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### **AMERICAS** (continued)

#### **Toronto**

Microchip Technology Inc. 5925 Airport Road, Suite 200 Mississauga, Ontario L4V 1W1, Canada Tel: 905-405-6279 Fax: 905-405-6253

#### ASIA/PACIFIC

#### China - Beijing

Microchip Technology, Beijing Unit 915, 6 Chaoyangmen Bei Dajie Dong Erhuan Road, Dongcheng District New China Hong Kong Manhattan Building Beijing, 100027, P.R.C. Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Shanghai

Microchip Technology Unit B701, Far East International Plaza, No. 317, Xianxia Road Shanghai, 200051, P.R.C.

Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### **Hong Kong**

Microchip Asia Pacific Unit 2101, Tower 2 Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2-401-1200 Fax: 852-2-401-3431

#### India

Microchip Technology Inc. India Liaison Office No. 6, Legacy, Convent Road Bangalore, 560 025, India Tel: 91-80-229-0061 Fax: 91-80-229-0062

#### Japan

Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122

#### Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea

Tel: 82-2-554-7200 Fax: 82-2-558-5934

### **ASIA/PACIFIC** (continued)

#### Singapore

Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850

Microchip Technology Taiwan 10F-1C 207 Tung Hua North Road Taipei, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

### **EUROPE**

#### Denmark

Microchip Technology Denmark ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

#### France

Arizona Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - Ier Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann-Ring 125 D-81739 München, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

#### Italy

Arizona Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### **United Kingdom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5858 Fax: 44-118 921-5835

Microchip received QS-9000 quality system certification for its worldwide headquarters design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

All rights reserved. © 2000 Microchip Technology Incorporated. Printed in the USA. 6/00 🙀 Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, except as maybe explicitly expressed herein, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.