# WHITLEY CEDAR ISLAND PLATFORM MESSAGE OF THE WEEK [MOW] UPDATE

**Intel Corporation Data Center Platform Application Engineering** WW19 2020 Document ID: 575523 **Intel Confidential**

### Legal Disclaimer

Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information. Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at Intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Warning: Altering PC clock or memory frequency and/or voltage may (i) reduce system stability and use life of the system, memory and processor; (ii) cause the processor and other system components to fail; (iii) cause reductions in system performance; (iv) cause additional heat or other damage; and (v) affect system data integrity. Intel assumes no responsibility that the memory, included if used with altered clock frequencies and/or voltages, will be fit for any particular purpose. Check with memory manufacturer for warranty and additional details.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <a href="http://www.intel.com/performance">http://www.intel.com/performance</a>.

Cost reduction scenarios described are intended as examples of how a given Intel- based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction.

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling, and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

Intel does not control or audit third-party benchmark data or the web sites referenced in this document. You should visit the referenced web site and confirm whether referenced data are accurate.

Intel® AMT should be used by a knowledgeable IT administrator and requires enabled systems, software, activation, and connection to a corporate network. Intel AMT functionality on mobile systems may be limited in some situations. Your results will depend on your specific implementation. Learn more by visiting Intel® Active Management Technology.

Intel is a sponsor and member of the Benchmark XPRT Development Community, and was the major developer of the XPRT family of benchmarks. Principled Technologies is the publisher of the XPRT family of benchmarks. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm. Intel, Intel<sup>®</sup> Optane<sup>™</sup>, Xeon, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2020, Intel Corporation. All Rights Reserved.

### Contents

| Section                        | Articles                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enabling                       | <u>Ice Lake Samples Sensitivity to VCCSA - Updates (Update) Page 5</u><br>Intel® Speed Select Technology Compliance Test for Ice Lake and Cooper Lake (New) Page 7                                                                                                                                                          |

| Documentation                  | <u>WW18'20 Ice Lake Heatmap (# 613226) Updates Now Available (Update) Page 19</u><br><u>Cedar Island Cooper Lake6 Pinlist – Final revision– RDC#601222-R1.0 (Update) Page 21</u><br><u>Whitley/Cedar Island Key Collateral Availability &amp; Forecast (Update) Page 23</u><br><u>Full Collateral List (Update) Page 24</u> |

| Tools and Debug                | Debug Tools Roadmap Update (New) Page 26<br>Integrated Channel Analysis Tool (ICAT) 4.200.15 Available (New) Page 39<br>Whitley Tools Update (Update) Page 41<br>Cedar Island Tool Update (Update) Page 53                                                                                                                  |

| OEM Communications<br>Feedback |                                                                                                                                                                                                                                                                                                                             |

| <u>Software</u>                |                                                                                                                                                                                                                                                                                                                             |

# ENABLING

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Reference Number: 575523 WW19 2020

Intel Confidential

# **ICE LAKE SAMPLES SENSITIVITY TO VCCSA -UPDATES**

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

### Ice Lake Samples Sensitivity to Vccsa - Updates

- Intel is seeing DC cycling failures with a small number of HCC ES1/ES2 parts. Typical failure signature is a DC cycling hang with **BL\_REQ\_RTID\_TABLE\_MISS** error. Failure is due to Vccsa sensitivity during reset, as an insufficient level of guardbanding was applied to ES manufacturing, leading to the issue seen.

- This issue is not expected to impact the board design.

- As the sensitivity occurs at boot time, we do not expect to have a work-around for HCC ES1/ES2. Since this sensitivity only occurs at boot time, Intel recommends that parts exhibiting this sensitivity to be re-allocated for non DC cycling activities.

- A fix has been identified to address the source of this sensitivity. This fix will be implemented starting with XCC ES1 & all subsequent Ice Lake HCC/XCC sample/production releases.

New

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

### Intel Speed Select Technology – Enabling efforts

Intel<sup>®</sup> Speed Select Technology feature: HOW TO

Avoid customer from trying various knobs in BIOS to use SST features.

### Collaterals ready at RDC doc id 621725:-

Intel<sup>®</sup> Speed Select Technology (Intel<sup>®</sup> SST) for Intel<sup>®</sup> Xeon<sup>®</sup> Processor (Ice Lake and Cooper Lake) Compliance Test Guide for Linux\* OS

Unique ID 621725

File Size: 1.04 MB

Last Updated: 04/30/2020

File Type: PDF File

CCL Usage Type: Targeted Version: 0.4

Content Type: Guides

Intel® Speed Select Technology (Intel® SST) for Intel® Xeon® Processor (Ice Lake and Cooper Lake) Compliance Test Guide for Linux\* OS

### Link to Compliance Test Demonstration:-

### http://10.5.250.47:8000/

# INTEL® SPEED SELECT TECHNOLOGY FEATURES: HOW TO

Intel and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

New

### Intel<sup>®</sup> Speed Select Technology (Intel<sup>®</sup> SST) Features

| Intel <sup>®</sup> SST-PP | Intel <sup>®</sup> SST-BF              | Intel <sup>®</sup> SST-CP | Intel <sup>®</sup> S |

|---------------------------|----------------------------------------|---------------------------|----------------------|

| Config 0                  | One set of HP/LP Cores and frequencies | Enable/Disable            | Bucket               |

|                           |                                        |                           | Bucket <sup>*</sup>  |

|                           |                                        |                           | Bucket               |

| Config 3                  | Not Available                          | Enable/Disable            | Bucket               |

|                           |                                        |                           | Bucket               |

|                           |                                        |                           | Bucket               |

| Config 4                  | Not Available                          | Enable/Disable            | Bucket               |

|                           |                                        |                           | Bucket <sup>•</sup>  |

|                           |                                        |                           | Bucket               |

### Note: Specific Feature Availability and number of available configurations are SKU specific

Intel<sup>®</sup> Speed Select Technology–Performance Profile (Intel<sup>®</sup> SST-PP)

Intel<sup>®</sup> Speed Select Technology–Base Frequency (Intel<sup>®</sup> SST-BF)

Intel<sup>®</sup> Speed Select Technology–Core Power (Intel<sup>®</sup> SST-CP)

Intel<sup>®</sup> Speed Select Technology–Turbo Frequency (Intel<sup>®</sup> SST-TF)

### SST-TF

- **0 HP Core Count**

- **1 HP Core Count**

- 2 HP Core Count

- 0 HP Core Count

- **1 HP Core Count**

- 2 HP Core Count

- 0 HP Core Count

- 1 HP Core Count

- 2 HP Core Count

### **BIOS** setting screen

| Override<br>SpeedStep (Pstates)<br>AVX P1<br>Intel SST-PP<br>Dynamic SST-PP   | <enable><br/><normal><br/><base/><br/><enable></enable></normal></enable> |                                    | Choose<br>in _PSD |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|-------------------|

| Intel SST-PP<br>Core Count<br>Current P1 Ratio [0<br>Package TDP (W)<br>Tjmax |                                                                           | Config 2<br>16<br>28<br>185<br>100 |                   |

| Activate SST-BF<br>Configure SST-BF<br>EIST PSD Function                      | <enable><br/><enable><br/>KHW_ALL&gt;</enable></enable>                   |                                    | U                 |

Intel Co<u>nfidential</u>

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

# \_ALL/SW\_ALL eturn

### BIOS Setting: for all Intel<sup>®</sup> Speed Select Technology Features

| Menu                    | Path                         | to Setting                                               | BIOS Setting                                                                                            | Requi             |

|-------------------------|------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------|

| Socket<br>Configuration | Advanced Power<br>Management | CPU P-State Control                                      | Intel <sup>®</sup> Advanced Vector Extensions<br>(Intel <sup>®</sup> AVX) License Pre-Grant Override    | D                 |

|                         |                              |                                                          | Enhance Intel Speed Step® Technology<br>(P-States)                                                      | E                 |

|                         |                              |                                                          | Intel <sup>®</sup> SST-PP                                                                               |                   |

|                         |                              |                                                          | Dynamic Intel <sup>®</sup> SST-PP                                                                       | E                 |

|                         |                              |                                                          | Activate Intel <sup>®</sup> SST-BF                                                                      | E                 |

|                         |                              |                                                          | Configure Intel <sup>®</sup> SST-BF                                                                     | E                 |

|                         |                              |                                                          | EIST PSD Function                                                                                       | Ϋ́Η               |

|                         |                              |                                                          | Boot Performance Mode                                                                                   | Maximum           |

|                         |                              |                                                          | Turbo Mode                                                                                              | E                 |

|                         |                              | Hardware PM State<br>Control                             | Hardware P-States                                                                                       | Native M<br>Legac |

|                         |                              | Frequency Prioritization                                 | Running Average Power Limit (RAPL)<br>Prioritization                                                    | E                 |

|                         |                              | CPU - Advanced PM<br>Tuning → Energy<br>Performance BIAS | Power Performance Tuning                                                                                | BIOS C            |

|                         |                              |                                                          | Platform Environment Control<br>Interface (PECI) Process Control<br>System (PCS) Energy Bias Hint (EPB) | OS Co             |

|                         |                              |                                                          | ENERGY_PERF_BIAS_CFG Mode                                                                               | Perf              |

|                         |                              |                                                          |                                                                                                         |                   |

### ired Setting

Disable

### Enable

Base Enable Enable Enable HW\_ALL m Performance Enable Mode with No acy Support

### Enable

**Controls EPB**

### Controls EPB

### rformance

Intel<sup>®</sup> Speed Select Technology–Performance Profile **BIOS** setting:

- Intel SST-PP = Base (this allow Intel SST-BF to functions)

- Intel SST-PP = Config1/Config2 (legacy) is equal to Config3/Config4 **E.g. QU98**

|              | Base   | Config1 =<br>Config3 | Config1<br>Config4 |

|--------------|--------|----------------------|--------------------|

| Active cores | 24     | 24                   | 16                 |

| P1 ratio     | 2.7GHz | 2.2GHz               | 2.8GHz             |

| TDP          | 220W   | 185W                 | 185W               |

Intel® SST-PP represents Intel® Speed Select Technology–Performance Profile

### Intel<sup>®</sup> Speed Select Technology–Performance Profile continued

Dynamic Intel<sup>®</sup> SST-PP: run time changes to Intel<sup>®</sup> SST-PP config level. **BIOS** setting:

- Intel SST-PP = Base (this allow Intel SST-BF to functions)

- Dynamic SST-PP = Enable.

OS steps: Use intel-speed-select app to control SST-PP config level

- intel-speed-select perf-profile get-lock-status (return 0) lacksquare

- intel-speed-select perf-profile set-config-level -l X –a (return success)

- X = config level = 0,3,4

- intel-speed-select perf-profile get-config-current-level (return X)

- Refer to 621725\_Intel-SST-for-Intel-Xeon-Processor\_Compliance-Test-Guide-for-Linux rev0p4: section 5.3.2 Intel<sup>®</sup> SST-PP: Functional for detail functional test instructions.

Intel® SST-PP represents Intel® Speed Select Technology–Performance Profile

### Intel<sup>®</sup> Speed Select Technology–Base Frequency (Intel<sup>®</sup> SST-BF)

**BIOS** setting:

- Intel SST-PP = Base (this allow Intel SST-BF to functions)

- Activate SST-BF

- **Configure SST-BF**

|              | Base (SST-BF off) | Base (SST-E |

|--------------|-------------------|-------------|

| Active cores | 24                | 8 HP cores  |

| P1 ratio     | 2.7GHz            | HP:2.9GHz + |

| TDP          | 220W              | 220W        |

OS steps: SST-BF enabling and disabling can be done using "intel-speed-select" app:

- intel-speed-select base-freq enable

- Refer to 621725 Intel-SST-for-Intel-Xeon-Processor Compliance-Test-Guide-for-Linux revOp4: section 5.3.6 Intel<sup>®</sup> SST-BF: Functional for detail functional test instructions.

### BF on)

### + 16 LP cores

### + LP:2.5GHz

### Intel<sup>®</sup> Speed Select Technology–Core Power (Intel<sup>®</sup> SST-CP) **BIOS Setting:**

- No specific Intel<sup>®</sup> SST-CP setting at BIOS menu.

- Frequency Prioritization -> Running Average Power Limit (RAPL) Prioritization -> Enable (This setting is a must for Intel<sup>®</sup> SST)

OS steps: "Intel-speed-select"

- intel-speed-select core-power enable (return success)

- Clos = class of service

- First config a clos:

- intel-speed-select core-power config -c 0 -n X -m Y

- Default all cores associated to clos id = 0; X = clos min in MHz; Y = clos max in MHz

- Refer to 621725 Intel-SST-for-Intel-Xeon-Processor Compliance-Test-Guide-for-Linux rev0p4: section 5.3.4 Intel<sup>®</sup> SST-CP: Functional for detail functional test instructions.

### Intel<sup>®</sup> Speed Select Technology–Turbo Frequency (Intel<sup>®</sup> SST-TF)

### **BIOS Setting:**

- No specific Intel<sup>®</sup> SST-CP setting at BIOS menu.

- Frequency Prioritization -> Running Average Power Limit (RAPL) Prioritization -> Enable (This setting is a must for Intel<sup>®</sup> SST)

OS steps: "Intel-speed-select"

- intel-speed-select turbo-freq enable (return success)

- intel-speed-select turbo-freq info –l 0 (return success)

- bucket 0,1,2's high-priority core count e.g. bucket 0 = 4 cores, bucket 1 = 12 cores, bucket 2 = 20 cores

- Associate cpu core to clos\_id:

- intel-speed-select --cpu 0-TOTAL CORES-1 core-power assoc -c 3 (make sure all call on low priority clos) ۲

- intel-speed-select --cpu 0-BUCKET0\_MINUS\_ONE core-power assoc -c 0 (make sure only bucket 0 count associate to high priority clos)

- Refer to 621725 Intel-SST-for-Intel-Xeon-Processor Compliance-Test-Guide-for-Linux rev0p4: section 5.3.8 Intel® • SST-TF: Functional for detail functional test instructions.

# DOCUMENTATION

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

# **WW18'20 ICE LAKE HEATMAP (# 613226) UPDATES NOW AVAILABLE**

New

Reference Number: 575523 WW19 2020

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

### Ice Lake Heatmap (#613226) Updates Now Available

WW18'20 Ice Lake Heatmap (#613226) Updates Now Available on RDC

New

Reference Number: 575523 WW19 2020

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Cooper Lake-6 pins are locked and no more changes are planned. The current revision – 0.75 is being promoted to 1.0 on RDC.

Release of Cooper Lake-6 pinlist (RDC#601222) Rev 1.0

Reference Number: 575523 WW19 2020

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Update

### Whitley/Cedar Island Key Collateral Availability & Forecast

| CPU Focus | Documents                | Doc #                                                                | 0.3    | 0.4 | 0.5                | 0.6    | .65x                           | 0.7               | 0.8                              | 0.9x               | 1                   | 1.5+ | 2                                       |

|-----------|--------------------------|----------------------------------------------------------------------|--------|-----|--------------------|--------|--------------------------------|-------------------|----------------------------------|--------------------|---------------------|------|-----------------------------------------|

| ICX       | Ice Lake EDS v1          | 574451                                                               | Aug'17 |     | Dec'17             | Feb'18 |                                | Jan'19            | WW09'20                          |                    | May'20              |      |                                         |

| ICX       | Ice Lake EDS v2          | 574942                                                               | Aug'17 |     | Jan'18             |        |                                | Jan'19            | WW10'20                          |                    | May'20              |      |                                         |

| ICX       | Ice Lake EDS v3          | 575291                                                               | Aug'17 |     | Feb'18             |        |                                | Jan'19            |                                  |                    | May'20              |      |                                         |

| CPX-6UPI  | Cooper Lake EDS v1       | 604785                                                               |        |     | Oct'18             |        |                                | WW34'19           |                                  |                    | May'20              |      |                                         |

| CPX-6UPI  | Cooper Lake EDS v2(A, B) | 604926<br>605073                                                     |        |     | Oct'18             |        |                                | Jul'19            |                                  |                    | Apr'20              |      |                                         |

| CPX-6UPI  | Cooper Lake EDS v3       | 603686                                                               |        |     | Nov'18             |        |                                | WW35'19           |                                  |                    | May'20              |      |                                         |

| ІСХ       | Socket P+ Pinlist        | 573771                                                               | Aug'17 |     | Dec'17             | Jan'18 |                                | Feb'18            | July'18<br>Rev 0.9<br>New Pinout |                    | Oct'18              |      |                                         |

| CPX-6UPI  | CPX-6UPI Pinlist         | 601222                                                               |        |     | Oct'18             |        |                                | Nov'18            |                                  |                    | Apr'20              |      |                                         |

| All       | Whitley PDG              | 574174                                                               | Aug'17 |     | Nov'17             | Feb'18 | Aug'18<br>(WW35)               | Oct'18            | Dec'18<br>(WW51)                 | Rev 0.9<br>WW41'19 | Q2'20               |      |                                         |

| CPX-6UPI  | PDG Addendum             | 604036                                                               |        |     |                    |        |                                | Nov'18            | WW06'19                          | Rev 0.9<br>Nov'19  | Q2'20               |      |                                         |

| All       | Whitley TMSDG            | 574080                                                               | Aug'17 |     | Q1'18              |        |                                | Dec'18<br>(w/CPX) | May'19                           |                    | Rev 1.01<br>Mar'20  |      |                                         |

| ICX       | Ice Lake BWG             | 594768                                                               | Mar'18 |     | Dec'18             |        |                                | Mar'2019          |                                  |                    | Apr'20              |      |                                         |

| CPX-6UPI  | Cooper Lake BWG          | 607480                                                               | Dec'18 |     | Feb'19             |        |                                | TBD               |                                  |                    | Mar'20              |      |                                         |

| ICX       | Whitley RAS IVG          | 614168                                                               | Aug'19 |     | Dec '19            |        |                                | Q2'20             |                                  |                    | Q3'20               |      |                                         |

| ісх       | Wilson City RP           | 575544 (sch)<br>575545 (brd)<br>613040 (sch-SMT)<br>613039 (brd-SMT) |        |     | Dec'17             |        | Aug'18<br>(WW34)<br>New Pinout | Oct'18<br>(WW43)  | Feb'19<br>(WW08'19)              |                    | Q4'19<br>Not Needed |      |                                         |

| CPX-6UPI  | Cooper City Modular RP   | 606823 (sch)<br>606817 (brd)                                         | Dec'18 |     |                    |        |                                | WW07'19           | WW22'19                          |                    | Not Needed          |      |                                         |

| ICX       | Orion City PC            | 576577                                                               |        |     | Feb'18             |        |                                | Sept'18           | WW06'19                          | WW28'19            | WW43'19             |      |                                         |

| ICX       | Tennessee Pass PC        | 613568                                                               |        |     | Combine w/ rev 0.7 |        |                                | Jun'19            |                                  |                    | Q2'20               |      |                                         |

| ІСХ       | Coyote Pass PC           | 613661                                                               |        |     | Combine w/ rev 0.7 |        |                                | Jul'19            |                                  |                    | Q2'20               |      |                                         |

| CPX-6UPI  | White Cloud City PC      | 610132 (sch)<br>610130 (brd)                                         | Feb'19 |     | Mar'19             |        |                                | May'19            | WW40'19                          |                    | Jan'20              |      |                                         |

| LBG/LBG-R | Lewisburg PCH EDS        | 547817                                                               |        |     |                    |        |                                |                   |                                  |                    |                     |      | Rev 2.6<br>Aug'19<br>Rev 3.0<br>WW13'20 |

| ICX       | Heatmap                  | 613226                                                               |        |     |                    |        |                                |                   |                                  |                    |                     |      |                                         |

| CPX6      | Heatmap                  | 618662                                                               |        |     |                    |        |                                |                   |                                  |                    |                     |      |                                         |

Collaterals currently available

Collaterals to be available in 2018

Collaterals to be available in 2019/2020 **RED BOLD TEXT**: updated info LBG represents Lewisburg UPI represents Intel<sup>®</sup> Ultra Path Interconnect (Intel<sup>®</sup> UPI); ICX represents Ice Lake; CPX represents Cooper Lake

Reference Number: 575523 WW19 2020

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

Update

### Full Collateral List

### Collateral list

\*\*Please be sure that you are signed in to access Technical Library content.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

# **TOOLS AND DEBUG**

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

New

Reference Number: 575523 WW19 2020

Intel Confidential

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

### Topics

- Key Points

- Tools Roadmaps by Segment

- **Overview of Features vs. Solution**

- Summary

- Debug Tools FAQs

### New

### Key Points in this Update

- Intel<sup>®</sup> System Debugger NDA ("White") is now the debug solution for NDA customers. Intel<sup>®</sup> Platform Validation Toolkit "White" capabilities merged into Intel<sup>®</sup> System Debugger NDA as of WW45 2019

- Intel, Lauterbach\* and Asset InterTech\* supporting DbC

- Asset fully owns integration testing, validation and support of Intel<sup>®</sup> System **Debugger NDA as necessary**

These foils address a complex topic and all considerations may not be represented.

If you have questions, please engage your Intel representative before making a debug tools strategy decision.

### Debug Tools Roadmap **Devices & Client**

| Empt<br>y | Not supported   |

|-----------|-----------------|

| ~         | Internal Valida |

| 0         | Additional solu |

| #         | ISD NDA (Whit   |

|                              | Intel <sup>®</sup> Lauterbach* |                   |                        |                 | *                           | Asset* |                       |                           |                         |  |

|------------------------------|--------------------------------|-------------------|------------------------|-----------------|-----------------------------|--------|-----------------------|---------------------------|-------------------------|--|

|                              |                                |                   |                        |                 | +                           |        | ASSE.                 | Asset                     |                         |  |

| Probe HW                     | ITP-<br>XDP3BR                 | Closed<br>Chassis | DCI.DbC<br>over        | DCI.DbC<br>over | CombiProbe V2               |        | Asset owns v<br>XDP3e | validation & su<br>(BSSB) | pport calls<br>over USB |  |

|                              |                                | Adapter<br>(CCA)  | USB USB DCI OOB MIPI60 |                 | MIPI60                      |        |                       |                           |                         |  |

|                              |                                |                   |                        |                 | (BSSB) (JTAG +<br>MIPI PTI) |        |                       |                           |                         |  |

| Lakefield 1 Dev              |                                | ✓                 | ✓                      | 0               | 0                           | 0      | #                     |                           | #                       |  |

| Comet Lake Client            | ✓                              | ✓                 | ✓                      | Ο               | 0                           | 0      | #                     | #                         | #                       |  |

| Ice Lake Client, Rocket Lake |                                | ✓                 | ✓                      | 0               | 0                           | 0      | #                     | #                         | #                       |  |

| Tiger Lake Client            | ✓                              | ✓                 | ✓                      | 0               | 0                           | 0      | #                     | #                         | #                       |  |

| Alder Lake Client            |                                | ✓                 | ✓                      | 0               | 0                           |        | #                     |                           | #                       |  |

| Elkhart Lake IOTG            |                                | ✓                 | ✓                      | Ο               | 0                           | 0      | #                     | #                         | #                       |  |

| Jasper Lake+                 | ✓                              | ✓                 | ✓                      | 0               | 0                           | 0      | #                     | #                         | #                       |  |

### Debug software from Intel (Intel<sup>®</sup> System Debugger NDA) can integrate with the Lauterbach<sup>\*</sup> and Asset<sup>\*</sup> transport solutions. Exception is the Lauterbach DCI.DbC transport solution which only works with Trace32.

ISS – Intel<sup>®</sup> System Studio

ISD - Intel<sup>®</sup> System Debugger - a component of Intel System Studio

PVT – Intel® Platform Validation Toolkit

ation POR & avail. to OEMs.

utions for OEMs or internal.

te) enabled, validated and supported by 3<sup>rd</sup> party

Intel probes from https://designintools.intel.com

### Debug Tools Roadmap uServer+

| Empt<br>y | Not supported              |

|-----------|----------------------------|

| ~         | Internal Valida            |

| 0         | Additional solu            |

| #         | ISD NDA (Whit              |

| &         | DCG or 3 <sup>rd</sup> par |

|                       | Intel®         |                                           |                     | Lauterbach*     |                   |                                       |                                       | Asset*        |               |                     |                |

|-----------------------|----------------|-------------------------------------------|---------------------|-----------------|-------------------|---------------------------------------|---------------------------------------|---------------|---------------|---------------------|----------------|

|                       |                |                                           | Q                   |                 | A                 | 14 8                                  |                                       | ASS.          | 2.see         |                     |                |

| Probe HW              | ITP-<br>XDP3BR | Closed<br>Chassis                         | DCI.DbC<br>over USB | DCI.DbC<br>over | CombiProbe V2     |                                       | QuadProbe                             | ECM-<br>XDP3e | CCC<br>(BSSB) | DCI.DbC<br>over USB | At-Sca<br>Debu |

| or<br>BS2/3<br>PPV    |                | Adapter T:Trace,<br>(CCA) X:DFx,<br>D:DMA |                     | USB             | DCI OOB<br>(BSSB) | <b>MIPI60</b><br>(JTAG +<br>MIPI PTI) | <b>MIPI60</b><br>(JTAG +<br>MIPI PTI) | Asset ov      | wns validat   | ion & suppo         | ort calls      |

| Ice Lake Server D     | ✓              | ✓                                         | ✓                   |                 | 0                 | 0                                     | 0                                     | #             | #             |                     | &              |

| Snow Ridge Server D   | ✓              | 1                                         | ✓ X                 |                 | ο                 | ο                                     | 0                                     |               |               |                     |                |

| Tanner Ridge Server D | ✓              | ✓                                         | ✓ X                 |                 | 0                 | 0                                     | 0                                     | #             | #             |                     | &              |

Debug software from Intel (Intel<sup>®</sup> System Debugger NDA) can integrate with the Lauterbach<sup>\*</sup> and Asset<sup>\*</sup> transport solutions. Exception is the Lauterbach DCI.DbC transport solution which only works with Trace32.

ISS – Intel<sup>®</sup> System Studio

ISD - Intel<sup>®</sup> System Debugger - a component of Intel System Studio

PVT – Intel<sup>®</sup> Platform Validation Toolkit

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

ation POR & avail. to OEMs.

utions for OEMs or internal.

te) enabled, validated and supported by 3<sup>rd</sup> party

rty distributed package of OpenIPC & ASD scripts

Intel probes from <a href="https://designintools.intel.com">https://designintools.intel.com</a>

### Debug Tools Roadmap Intel<sup>®</sup> Xeon<sup>®</sup> Server

| Empt<br>y | Not supported              |

|-----------|----------------------------|

| ~         | Internal Valida            |

| 0         | Additional solu            |

| #         | ISD NDA (Whit              |

| &         | DCG or 3 <sup>rd</sup> par |

### Intel probes from https://designintools.intel.com

|                              | Intel®           |                         |                             |                   |          | Laut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | erbach*                        | Asset*                         |                              |       |                      |

|------------------------------|------------------|-------------------------|-----------------------------|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|------------------------------|-------|----------------------|

|                              |                  | 4                       |                             |                   |          | Con the second s | 14 8                           |                                | ALSO A                       | Asser |                      |

|                              | XDP3BR or        |                         | DCI.DbC<br>over USB         | At-Scale<br>Debug | over USB | CombiProbe V2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                | QuadProbe ECM-<br>XDP3e        |                              |       | DCI. DbC<br>over USB |

|                              | BS2/3 for<br>PPV | <b>Adapter</b><br>(CCA) | T:Trace,<br>X:DFx,<br>D:DMA |                   |          | DCI OOB<br>(BSSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MIPI60<br>(JTAG +<br>MIPI PTI) | MIPI60<br>(JTAG +<br>MIPI PTI) | Asset owns validation & supp |       |                      |

| Cooper Lake, Cascade Lake AP | ✓                | ✓                       | ✓ T,D                       | &                 | 0        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                              | 0                              | #                            | #     |                      |

| Ice Lake Server SP           | ✓                | 1                       | ✓ T,D                       | &                 | 0        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                              | 0                              | #                            | #     |                      |

| Rocket Lake S Server         | ✓                | ✓                       | $\checkmark$                |                   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |                                | #                            | #     | #                    |

| Ash Creek Falls              | ✓                |                         | $\checkmark$                |                   |          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                              | 0                              |                              |       |                      |

| Sapphire Rapids SP           | ✓                | ✓                       | $\checkmark$                | &                 | Ο        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                              | 0                              | #                            | #     | #                    |

Debug software from Intel (Intel<sup>®</sup> System Debugger NDA) can integrate with the Lauterbach<sup>\*</sup> and Asset<sup>\*</sup> transport solutions. Exception is the Lauterbach DCI.DbC transport solution which only works with Trace32.

ISS - Intel<sup>®</sup> System Studio

ISD – Intel<sup>®</sup> System Debugger - a component of Intel System Studio

PVT – Intel<sup>®</sup> Platform Validation Toolkit

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

- ation POR & avail. to OEMs.

- utions for OEMs or internal.

- te) enabled, validated and supported by 3<sup>rd</sup> party

- ty distributed package of OpenIPC & ASD scripts

### **Overview of Features vs. Solution**

| Capability                                                             | Intel<br>XDP3b<br>``the blue<br>box'' | Intel<br>Direct<br>Connect<br>Interface<br>(DCI) | Intel® At Scale<br>Debug<br>BMC-JTAG * | Intel® At Scale<br>Debug<br>BMC-PECI              | Lauterbach<br>CombiProbe +<br>PowerTrace | Lauterbach<br>Combiprobe | Lauterbach<br>QuadProbe<br>+<br>PowerTrac<br>e | Lauterbach<br>Quadprobe     | Lauterbach<br>DbC     | ASSET<br>InterTech<br>SourcePoin<br>t | ASSET<br>InterTech<br>ScanWorks<br>Embedded<br>Diagnostics |

|------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|----------------------------------------|---------------------------------------------------|------------------------------------------|--------------------------|------------------------------------------------|-----------------------------|-----------------------|---------------------------------------|------------------------------------------------------------|

| Common Usage Model                                                     | Power on,<br>bench debug              | Bench Debug                                      | Deployed<br>Debug                      | Autonomous<br>& Interactive<br>data<br>collection | Power on,<br>bench debug                 | Power on,<br>bench debug | Power on,<br>bench debug                       | Power on,<br>bench<br>debug | Bench<br>debug        | Power on,<br>bench debug              | Deployed<br>Debug                                          |

| Closed or Open Chassis                                                 | Open<br>Chassis                       | Closed<br>Chassis                                | Closed<br>Chassis                      | Closed<br>Chassis                                 | Open Chassis                             | Open/Closed<br>Chassis   | Open<br>Chassis                                | Open<br>Chassis             | Closed<br>Chassis     | Open/Closed<br>Chassis                | Closed<br>Chassis                                          |

| Adapter/Interface                                                      | XDP60**                               | USB2/BSSB                                        | BMC                                    | BMC                                               | MIPI60                                   | MIPI60 and<br>BSSB       | MIPI60                                         | MIPI60                      | USB2                  | XDP60**,<br>USB2 and<br>BSSB          | BMC                                                        |

| # Of Sockets                                                           | up to 8                               | up to 8                                          | up to 8                                | up to 8                                           | up to 8                                  | up to 8                  | up to 32**                                     | up to 32**                  | up to 8               | up to 8                               | up to 8                                                    |

| Access Method                                                          | Local Host                            | Local Host                                       | Remote Host                            | Remote Host                                       | Local Host                               | Local Host               | Local Host                                     | Local Host                  | Local Host            | Local Host                            | Remote Host                                                |

| Source Level Debug                                                     | Yes                                   | Yes                                              | No                                     | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | Yes                   | Yes                                   | Ask Asset                                                  |

| CPU Run Control & architectural debug                                  | Yes                                   | Yes                                              | Yes                                    | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | Yes                   | Yes                                   | Yes                                                        |

| PVT Integration                                                        | Yes                                   | Yes                                              | Yes                                    | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | No                    | Yes                                   | Yes                                                        |

| CPU & PCH Register Access (Cscripts)                                   | Yes                                   | Yes                                              | Yes                                    | Yes                                               | Yes                                      | Yes                      | Yes                                            | Yes                         | No                    | Yes                                   | Yes                                                        |

| Error Injection (Cscripts)                                             | Yes                                   | Yes                                              | Yes                                    | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | No                    | Yes                                   | Yes                                                        |

| System Event Detection/Injection (reset,<br>powergood,<br>etc.)        | Yes                                   | Yes                                              | Yes                                    | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | Yes                   | Yes                                   | Yes                                                        |

| Red Cover Unlock with Intel Employee<br>Present                        | Yes                                   | Maybe/Yes                                        | Yes                                    | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | No                    | Yes                                   | Yes                                                        |

| Red Cover Unlock PCH Early Break (halt PCH),<br>Intel Employee present | Yes                                   | No/Yes                                           | No                                     | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | No                    | Yes                                   | No                                                         |

| DMA Write/Read into/out of Memory                                      | No                                    | Yes                                              | No                                     | No                                                | No                                       | No                       | No                                             | No                          | Yes                   | No                                    | No                                                         |

| System Tracing with Intel® Trace Hub                                   | Yes                                   | Yes                                              | Yes*                                   | No                                                | Yes                                      | Yes                      | Yes                                            | Yes                         | Yes                   | Yes                                   | Yes                                                        |

| PTI Trace (Live Streaming)                                             | No                                    | No                                               | No                                     | No                                                | Yes                                      | Yes                      | Yes                                            | No                          | No                    | No                                    | No                                                         |

| HW Device Listed Price (US Dollars)                                    | \$900                                 | \$390                                            | Reference<br>Platform BOM              | Reference<br>Platform BOM                         | Contact<br>Lauterbach                    | Contact<br>Lauterbach    | Contact<br>Lauterbach                          | Contact<br>Lauterbach       | Contact<br>Lauterbach | Contact<br>ASSET                      | Contact<br>ASSET                                           |

| SW Licensing Cost                                                      | PVT/ISS<br>License                    | PVT/ISS<br>License                               | PVT/ISS<br>License                     | PVT/ISS<br>License                                | Contact<br>Lauterbach                    | Contact<br>Lauterbach    | Contact<br>Lauterbach                          | Contact<br>Lauterbach       | Contact<br>Lauterbach | Contact<br>ASSET                      | Contact<br>ASSET                                           |

\* Trace to memory. (Trace pins are not routed to BMC GPIOs per the white paper)

\*\* For any designs above 8 sockets, contact an Intel FAE.

\*\*\* Reduced bandwidth. 1.6 Gbit/s on 8 bit port

inte

### Summary

- 14nm designs using OpenIPC in Intel<sup>®</sup> System Debugger for internal and external customers such as OxMs

- Intel System Debugger, a component of Intel<sup>®</sup> System Studio, is now the go to solution for system level debug. Intel<sup>®</sup> PVT "White" capabilities merged as of WW45'19 into Intel System Debugger NDA.

- ITP II (DAL) is in sustaining mode, no new features, Q3 2019

- Intel, Lauterbach and Asset InterTech supporting DbC

### DCI.DbC

### **DAES** Contacts

### **Tools Support**

- Debugtoolssupport@intel.com

- http://goto/debugtoolssupport

### **Downloads**

- http://goto.intel.com/downloadcenter

- Goto/pvt

### **IAGS/CPDP** Contacts

### **Tools Support**

intelsystemstudio@intel.com lacksquare

### **Downloads**

oductid=2336

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. Copyright © 2020, Intel Corporation.

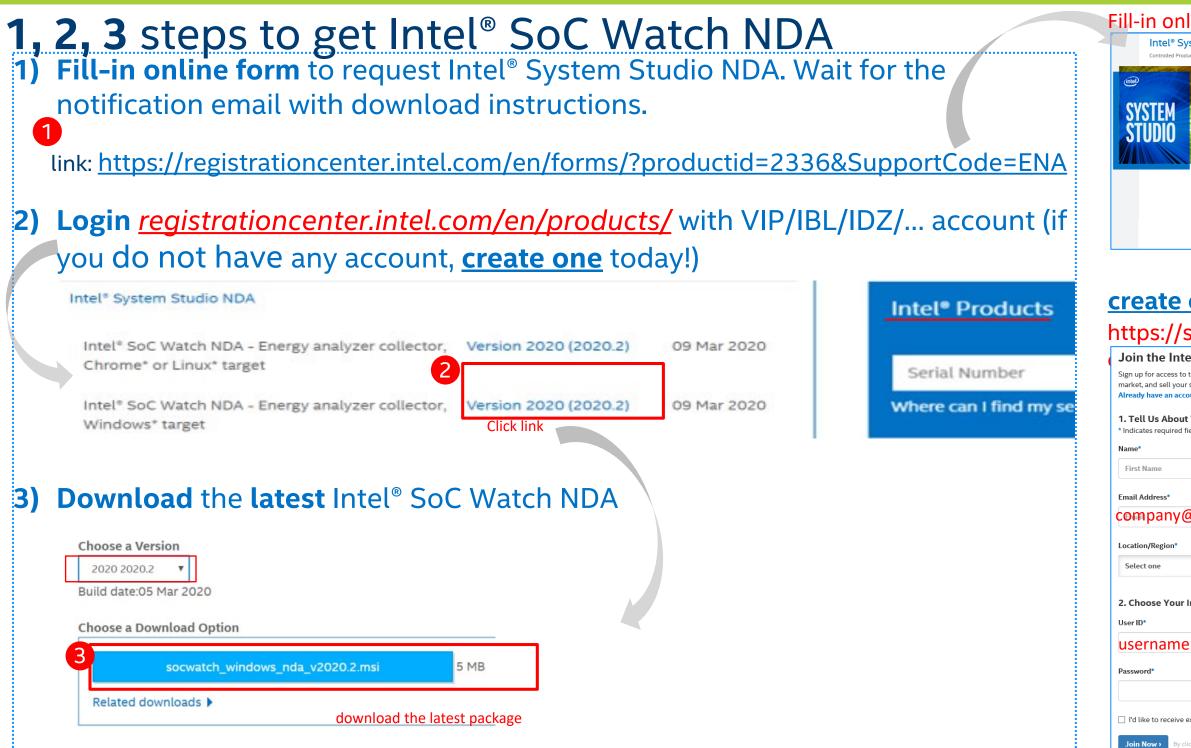

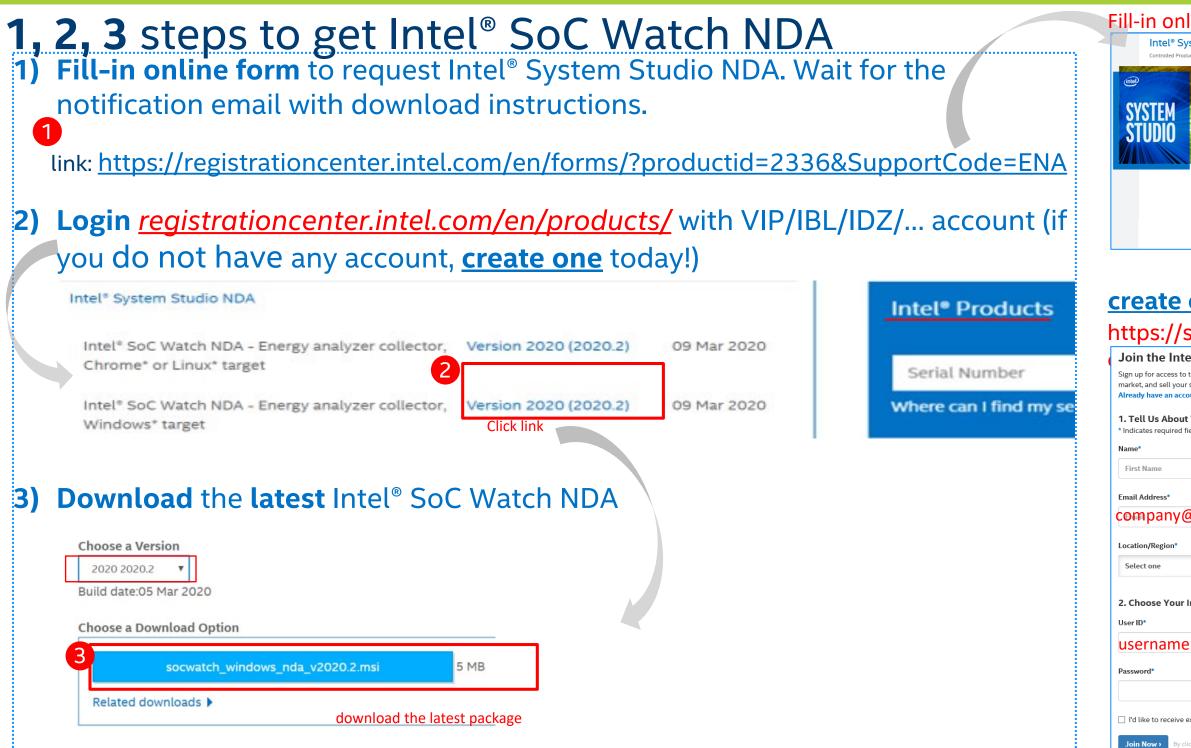

### https://registrationcenter.intel.com/en/forms/?pr

### Debug Tools FAQs

### Has Intel<sup>®</sup> In-Target Probe (Intel<sup>®</sup> ITP) PDT (DAL) software been EOL'd? 1. The Intel<sup>®</sup> ITP PDT (DAL) software product is feature complete and is in sustaining status as of Q3 A:

2019. It continues to be available and supported for current customers on client and server programs as detailed in the Debug Tools Roadmap.

### 2. Can I still order Intel<sup>®</sup> ITP PDT (DAL) software?

- A: Customers can continue to obtain licenses for Intel<sup>®</sup> ITP PDT (DAL) software through the Design-In Tools website (<u>https://designintools.intel.com</u>). Since there is not additional development planned after H1 2019, there is no longer a cost.

- Is there a replacement software debug suite for the Intel<sup>®</sup> ITP PDT (DAL) 3. software?

- Yes, there are several options from multiple vendors, e.g. Intel (Intel<sup>®</sup> System Debugger), Asset A: InterTech\* or Lauterbach\*, which support multiple transport options including DCI DbC, DCI OOB, MIPI60 and legacy XDP60 as detailed in the Debug Tools Roadmap; goto/debugtoolsroadmap

### Debug Tools FAQs continued

### What is Intel<sup>®</sup> System Studio? 4.

Intel<sup>®</sup> System Studio is a development tools suite that provides system debug & trace, system A: power/thermal & performance analysis, and build tools. The tools are intended for OxMs, SIs and other customers that are involved in system bring-up, platform enabling & validation, and general development of products based on Intel® Architecture.

### What is Intel<sup>®</sup> System Debugger? 5.

Intel<sup>®</sup> System Debugger, a component of Intel<sup>®</sup> System Studio, is ideal for platform bring-up A: and debugging of hardware, firmware, EFI/UEFI BIOS, operating systems, and device drivers. It allows debug of Windows\* and Linux\* kernel sources, and dynamically loaded drivers and kernel modules. Intel<sup>®</sup> System Debugger provides system debug & trace capabilities including a source level debugger, system trace based on Intel<sup>®</sup> Trace Hub, Crash Log analysis, Python\* scripting, OS aware debugging, CScripts, and more. For Windows\* target development it provides the Intel<sup>®</sup> Debug Extensions for WinDbg\* which enables JTAG Debug & Trace for Microsoft\* Windows\* system, device driver and UEFI development. A developer can perform JTAG-based debug and trace over low-cost USB\* connections or use a traditional JTAG probe.