US012314644B2

# (12) United States Patent

Patidar et al.

# (54) INTEGRATED CIRCUIT DESIGN METHOD, SYSTEM AND COMPUTER PROGRAM PRODUCT

(71) Applicants: TAIWAN SEMICONDUCTOR

MANUFACTURING COMPANY,

LTD., Hsinchu (TW); TSMC

NANJING COMPANY, LIMITED,

Nanjing (CN)

(72) Inventors: Ankita Patidar, Hsinchu (TW); Sandeep Kumar Goel, Hsinchu (TW); Yun-Han Lee, Hsinchu (TW)

(73) Assignees: TAIWAN SEMICONDUCTOR

MANUFACTURING COMPANY,

LTD., Hsinchu (TW); TSMC

NANJING COMPANY, LIMITED,

Nanjing (CN)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 18/356,426

(22) Filed: Jul. 21, 2023

(65) Prior Publication Data

US 2023/0376660 A1 Nov. 23, 2023

#### Related U.S. Application Data

(63) Continuation of application No. 17/836,954, filed on Jun. 9, 2022, now Pat. No. 11,727,177, which is a (Continued)

#### (30) Foreign Application Priority Data

Nov. 3, 2020 (CN) ...... 202011207868.0

(10) Patent No.: US 12.314.644 B2

(45) **Date of Patent:** \*May 27, 2025

(51) **Int. Cl. G06F 30/327 G06F 30/3308**(2020.01)

(Continued)

(58) Field of Classification Search

CPC .. G06F 30/327; G06F 30/398; G06F 30/3308; G06F 30/333; G06F 2119/18; G06F 2119/02

(Continued)

### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,621,201 A 5,812,561 A 11/1986 Amdahl et al. 5,812,561 A (Continued)

#### FOREIGN PATENT DOCUMENTS

KR 2018111126 10/2018

Primary Examiner — Phallaka Kik

(74) Attorney, Agent, or Firm — Hauptman Ham, LLP

# (57) ABSTRACT

A method includes creating a plurality of groups of paths from a plurality of paths in an integrated circuit (IC) layout diagram. Each group has a unique dominant feature among a plurality of features of the plurality of paths. The method further includes testing a path in a group and, when the path fails, modifying at least one of the IC layout diagram, at least a portion of at least one library having cells included in the IC layout diagram, or a manufacturing process for manufacturing an IC corresponding to the IC layout diagram. The plurality of features includes a numerical feature having a numerical value, and a categorical feature having a nonnumerical value. The non-numerical value is converted into a converted numerical value. The plurality of groups is created based on the numerical value of the numerical (Continued)

# **US 12,314,644 B2**Page 2

| featu<br>featu | re, and the converted numerical value of the categorical re.                                                                 | 7,260,442 B2<br>9,256,709 B2<br>9,939,880 B1                                                    | 2/2016<br>4/2018                                 | Hwang et al.<br>Yu et al.<br>Foreman et al.                 |

|----------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|

|                | 20 Claims, 14 Drawing Sheets                                                                                                 | 10,592,625 B1<br>10,846,453 B1<br>11,361,248 B2<br>11,372,551 B2<br>11,379,643 B2               | 11/2020<br>6/2022<br>6/2022<br>7/2022            | Huang et al.<br>Choi et al.<br>Patidar et al.               |

|                | Related U.S. Application Data                                                                                                | 11,727,177 B2*                                                                                  | 8/2023                                           | Patidar G06F 30/398 716/136                                 |

| (51)           | continuation of application No. 17/122,769, filed on Dec. 15, 2020, now Pat. No. 11,379,643.  Int. Cl. G06F 30/333 (2020.01) | 12,008,452 B2 * 2003/0131328 A1 2004/0250230 A1 2006/0242502 A1 2007/0011542 A1 2009/0031269 A1 | 7/2003<br>12/2004<br>10/2006<br>1/2007<br>1/2009 | Itou et al. Wang et al. Mukherjee et al. Chen et al.        |

|                | G06F 30/398 (2020.01)<br>G06F 119/02 (2020.01)<br>G06F 119/18 (2020.01)                                                      | 2009/0240458 A1<br>2009/0276191 A1<br>2010/0242011 A1<br>2011/0121838 A1                        | 11/2009<br>9/2010                                | Desineni et al. Bell, Jr. et al. Mukai et al. Gillis et al. |

| (52)<br>(58)   | U.S. Cl. CPC G06F 30/333 (2020.01); G06F 2119/02 (2020.01); G06F 2119/18 (2020.01)  Field of Classification Search           | 2012/0047412 A1<br>2012/0047413 A1<br>2014/0040838 A1<br>2014/0282342 A1                        | 9/2014                                           | Chung<br>Liu et al.<br>Wu et al.                            |

| (36)           | USPC                                                                                                                         | 2015/0278429 A1<br>2017/0371983 A1<br>2019/0087388 A1<br>2019/0220776 A1                        | 3/2019<br>7/2019                                 | Franch et al.<br>Venturelli et al.<br>Huang et al.          |

| (56)           | References Cited                                                                                                             | 2020/0042663 A1<br>2020/0125696 A1<br>2020/0134121 A1                                           |                                                  | Chang et al. Lin et al.                                     |

|                | U.S. PATENT DOCUMENTS                                                                                                        | 2021/0034251 A1<br>2022/0067250 A1                                                              | 2/2021<br>3/2022                                 | Choi et al.<br>Chakrabarty et al.                           |

|                | 6,223,097 B1 4/2001 Hashimoto et al.<br>6,519,749 B1 2/2003 Chao et al.<br>6,779,162 B2 8/2004 Barrick                       | 2022/0215146 A1 * cited by examiner                                                             |                                                  | Lin et al.                                                  |

16.3A

May 27, 2025

May 27, 2025

Fig. 3G

| possession of                                      |

|----------------------------------------------------|

| £4.)                                               |

| Q,C                                                |

| - <del>, , , , , , , , , , , , , , , , , , ,</del> |

Clock re-convergence pessimism

| MICAL FEATURES                                  | PHYSICAL FEATURES                                    |

|-------------------------------------------------|------------------------------------------------------|

| rt-point pin name                               | Xspan of path                                        |

| thoini cell function type                       | Yspan of path                                        |

| p,memory, input)                                | Area covered by path                                 |

| rt point cell physical type                     | Number of vias in path                               |

| d point pin name                                | Total physical net length                            |

| d point cell function type<br>p. memory, input) | Physical net length in metal layer M0/1/2/3          |

| d point cell physical type                      | Number of transistors in cells                       |

| gic depth of path                               | <del>Cell pin orientations</del>                     |

| unch clock name                                 | Number of cells based on height                      |

| nure clock name                                 | of cells                                             |

| mber of VT cells in path                        | Number of cells based on pitch                       |

| /T/LVT/ULVT)                                    | Number of layout shapes in path                      |

| mber of cells with driving                      | (L. I, T)                                            |

| mgth D1/2/3/                                    | VT density in physical                               |

| mber of cells based on number nputs 1/2/3       | neighborhood of path (in user<br>defined window)     |

| mber of cells based on number<br>outputs 1/2/3  | Congestion in physical neighborhood of path (in user |

| mber of cells based on logic                    | uemica wanaw <i>)</i>                                |

| c (AOI, AND, XOR, OR Etc.)                      |                                                      |

Feature Encoding & Reduction

Feature Extraction

Feature Clustering

154

| <br>TIMING FEATURES                     | LOGICALFI            |

|-----------------------------------------|----------------------|

| Clock-uncertainty in its                | Start point pin na   |

| Library setup/hold time                 | Start moint cell fin |

| Input delay                             | (flop,memory, in     |

| Output delay                            | Start point cell ph  |

| Delay due to SI (signal arrival)        | End point pin nan    |

| Default path group name                 | End point cell fun   |

| Data path delay with buffer/            | (flop, memory, in    |

| inverter                                | End point cell phy   |

| Data path delay without buffer          | Logic depth of pa    |

| inverter                                | Launch clock nan     |

| Net delay                               | Capture clock nan    |

| Sensitivity delay of cells              | Number of VT ce      |

| Capture clock period                    | (SVT/LVT/ULV)        |

| Capture latency                         | Number of cells v    |

| Launch latency                          | strength D1/2/3/     |

| Launch clock edge                       | Number of cells b    |

| Capture clock edge                      | of inputs 1/2/3      |

| Instance with smallest slew-ratio       | Number of cells b    |

| Cell-input-siew/cell-output-siew        | of outputs 1/2/3     |

| Net with smallest slew-ratio            | Number of cells b    |

| Net-input-slew/net-output-slew          | type (AOL, AND,      |

| <br>Fanout of net with smallest         |                      |

| <br>stew-rano                           |                      |

| <br>Cap of net with smallest slew ratio |                      |

| <br>Słack                               |                      |

|                                         |                      |

Cluster Analysis and Path Grouping

ATPG

Hig. 4

F19.5

i L

# INTEGRATED CIRCUIT DESIGN METHOD. SYSTEM AND COMPUTER PROGRAM **PRODUCT**

#### RELATED APPLICATION(S)

The present application is a continuation application of U.S. patent application Ser. No. 17/836,954, filed Jun. 9, 2022, now U.S. Pat. No. 11,727,177, Aug. 15, 2023, which is a continuation application of U.S. patent application Ser. No. 17/122,769, filed Dec. 15, 2020, now U.S. Pat. No. 11,379,643, issued Jul. 5, 2022, which claims the priority of China Application No. 202011207868.0, filed Nov. 3, 2020. The above-referenced patents and applications are incorpo

15 embodiments. rated herein by reference in their entireties.

#### BACKGROUND

An integrated circuit (IC) typically includes a number of 20 semiconductor devices represented in an IC layout diagram. An IC layout diagram is hierarchical and includes modules which carry out higher-level functions in accordance with the semiconductor device's design specifications. The modules are often built from a combination of cells, each of 25 accordance with some embodiments. which represents one or more semiconductor structures configured to perform a specific function. Cells having pre-designed layout diagrams, sometimes known as standard cells, are stored in standard cell libraries (hereinafter "libraries" or "cell libraries" for simplicity) and accessible by 30 various tools, such as electronic design automation (EDA) tools, to generate, optimize and verify designs for ICs. At various steps during the IC design process, various checking and testing are performed to make sure that ICs can be made and will function as designed.

# BRIEF DESCRIPTION OF THE DRAWINGS

Aspects of the present disclosure are best understood from the following detailed description when read with the 40 accompanying figures. It is noted that, in accordance with the standard practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

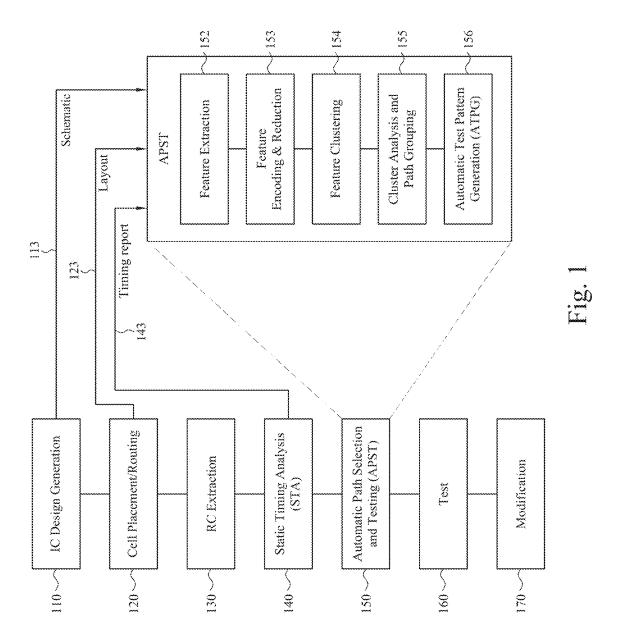

FIG. 1 is a functional flow chart of at least a portion of an IC design flow, in accordance with some embodiments.

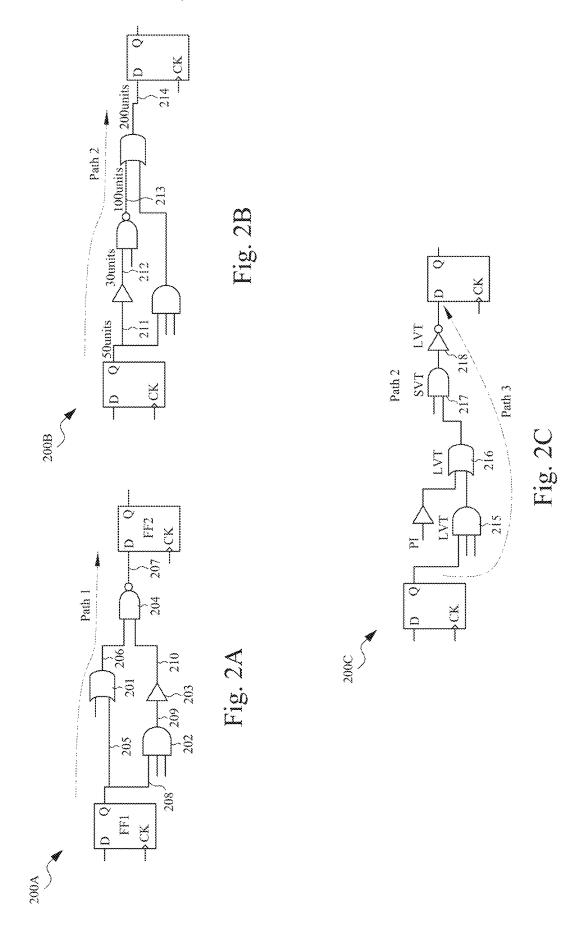

FIGS. 2A-2F are schematic logic diagrams of various sections of an IC layout diagram with example paths, in accordance with some embodiments.

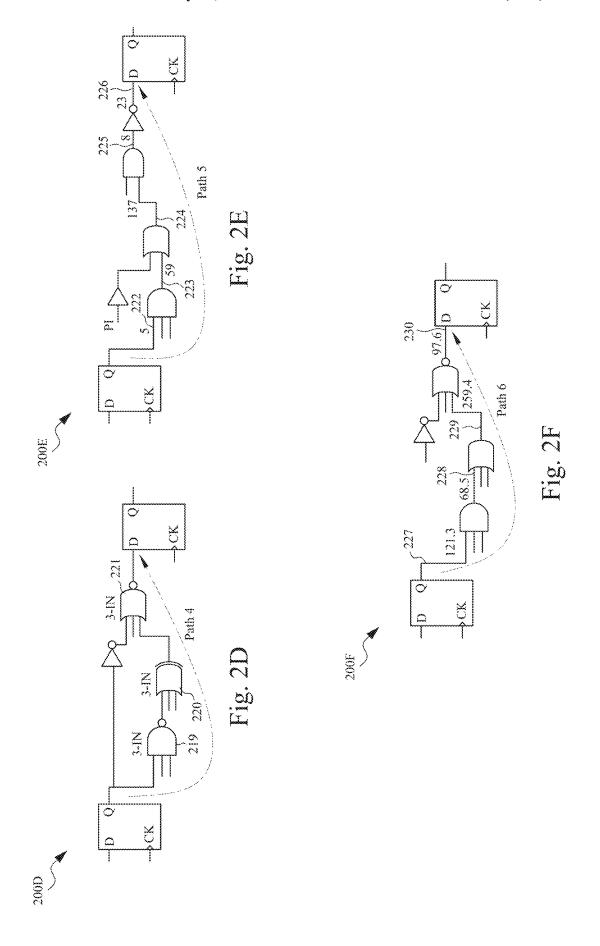

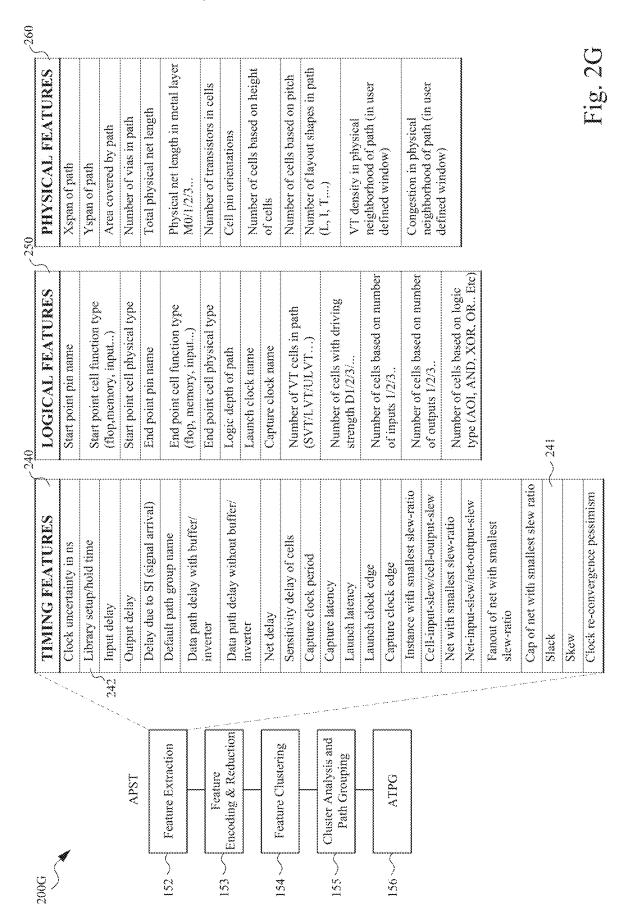

FIG. 2G is a schematic view of various extracted features of paths in an IC layout diagram, in accordance with some

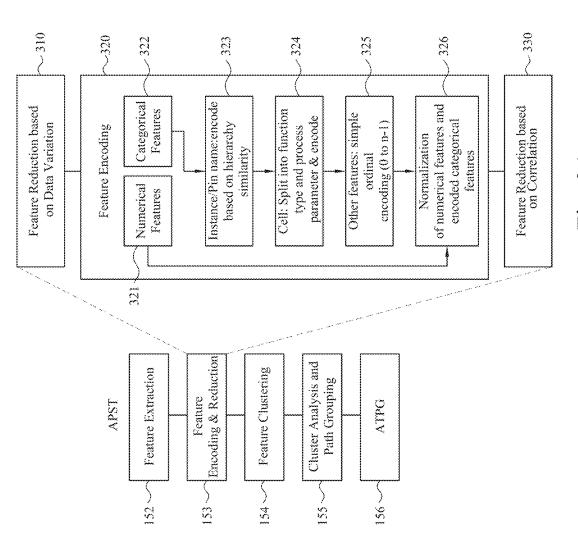

FIG. 3A is a flow chart of a process in a feature encoding and reduction operation, in accordance with some embodi- 55

FIG. 3B is a schematic data representation of example features in a first feature reduction operation, in accordance with some embodiments.

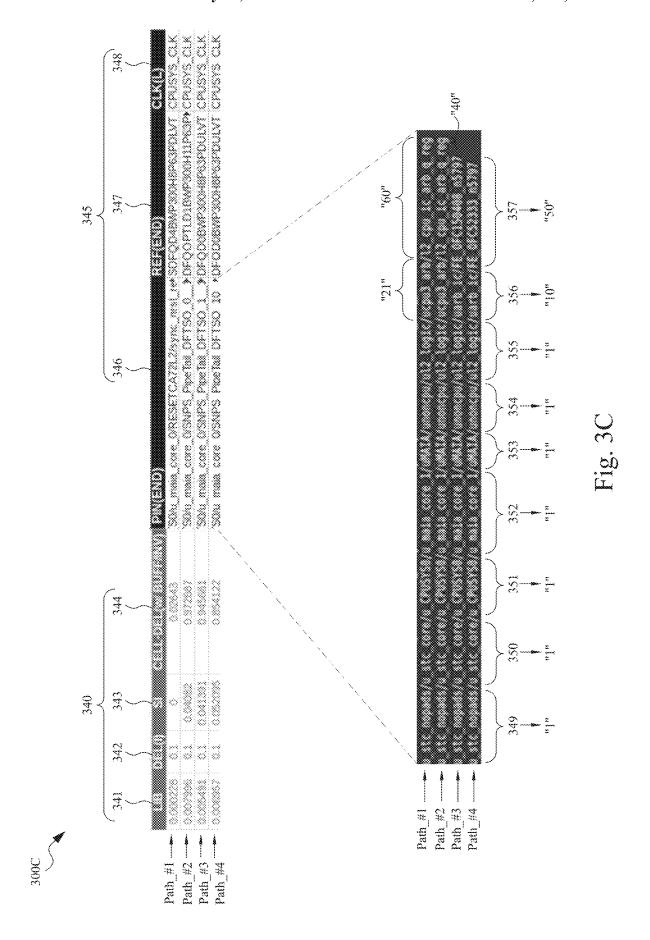

FIG. 3C is a schematic view of a table including various 60 numerical features and categorical features with corresponding values in several example paths in a first encoding operation, in accordance with some embodiments.

FIG. 3D is a schematic view of a table including an example feature with corresponding values in several 65 example paths in a second encoding operation, in accordance with some embodiments.

2

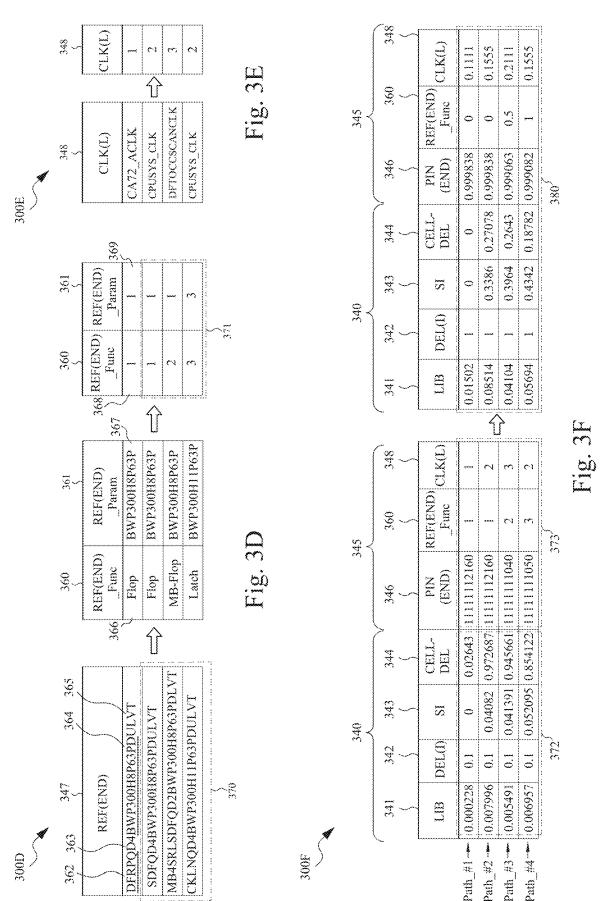

FIG. 3E is a schematic view of a table including an example feature with corresponding values in several example paths in a third encoding operation, in accordance with some embodiments.

FIG. 3F is a schematic view of a table including various numerical features and categorical features with corresponding values in several example paths in a normalization operation, in accordance with some embodiments.

FIG. 3G is a schematic view of a table including various features with corresponding correlation coefficients in a second feature reduction operation, in accordance with some embodiments.

FIG. 3H is a schematic view of a reduced set of features of paths in an IC layout diagram, in accordance with some

FIG. 4 is a flow chart of a process in feature clustering and path grouping operations, in accordance with some embodi-

FIG. 5 is a flow chart of a process, in accordance with some embodiments.

FIG. 6 is a block diagram of an EDA system, in accordance with some embodiments.

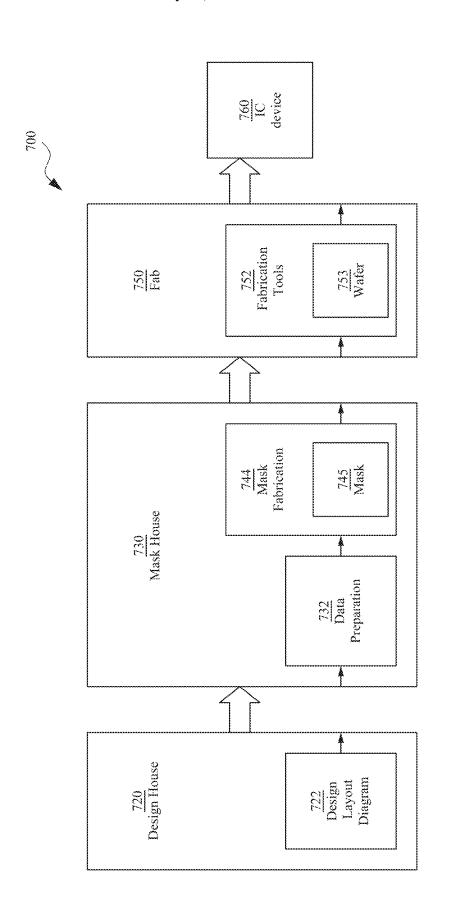

FIG. 7 is a block diagram of an IC manufacturing system and an IC manufacturing flow associated therewith, in

# DETAILED DESCRIPTION

The following disclosure provides many different embodiments, or examples, for implementing different features of the provided subject matter. Specific examples of components, materials, values, steps, operations, materials, arrangements, or the like, are described below to simplify the present disclosure. These are, of course, merely 35 examples and are not intended to be limiting. Other components, values, operations, materials, arrangements, or the like, are contemplated. For example, the formation of a first feature over or on a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed between the first and second features, such that the first and second features may not be in direct contact. In addition, the present disclosure may repeat reference numerals and/or letters in the various examples. This repetition is for the purpose of simplicity and clarity and does not in itself dictate a relationship between the various embodiments and/or configurations discussed.

Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. The apparatus may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accord-

In an IC design process, one or more pre-manufacturing or post-manufacturing verifications are performed for identifying a potential fault in an IC layout diagram or in an IC (chip) manufactured in accordance with the IC layout diagram. In some embodiments, a plurality of paths in an IC layout diagram is grouped into a plurality of groups. The paths in each group share a common dominant feature, such as a timing feature, a logical feature, or a physical feature.

A test is performed for at least one path in each group. When a path fails the test, the dominant feature associated with the corresponding group is identified as related to a systematic defect. Based on the dominant feature identified as related to a systematic defect, a correction for fixing the failing path is made to at least one of the IC layout diagram, a library having cells included in the IC layout diagram, or a manufacturing process. As a result, in at least one embodiment, it is possible to fix or improve multiple paths sharing the same dominant feature by a common correction strategy. In one or more embodiments, by grouping paths by dominant features for testing, it is possible to identify and correct various systematic defects which are not identified in other approaches.

FIG. 1 is a functional flow chart of at least a portion of an IC design flow 100 in accordance with some embodiments. The IC design flow 100 utilizes one or more electronic design automation (EDA) tools for generating, optimizing and/or verifying a design of an IC before and/or after 20 manufacturing the IC. The EDA tools, in some embodiments, are one or more sets of executable instructions for execution by a processor or controller or a programmed computer (e.g., system 600 (FIG. 6)) to perform the indicated functionality. In at least one embodiment, the IC 25 design flow 100 is performed by a design house of an IC manufacturing system discussed herein with respect to FIG.

At IC design generation operation 110, a design of an IC is provided by a circuit designer. In some embodiments, the 30 design of the IC comprises an IC schematic, i.e., an electrical diagram, of the IC. In some embodiments, the schematic is generated or provided in the form of a schematic netlist, such as a Simulation Program with Integrated Circuit Emphasis (SPICE) netlist. Other data formats, e.g., Verilog, 35 for describing the design are usable in some embodiments. In some embodiments, a pre-layout simulation is performed on the design to determine whether the design meets a predetermined specification. When the design does not meet the predetermined specification, the IC is redesigned. In at 40 least one embodiment, a pre-layout simulation is omitted.

At cell placement and routing operation 120, a layout diagram of the IC is generated based on the IC schematic. The cell placement and routing operation 120 is referred to as Automatic Placement and Routing (APR) in at least one 45 embodiment. The IC layout diagram comprises physical positions of various circuit elements of the IC as well as physical positions of various nets interconnecting the circuit elements. For example, the IC layout diagram is generated in the form of a Graphic Design System (GDS) file. Other 50 data formats, e.g., Design Exchange Format (DEF), for describing the design of the IC are within the scope of various embodiments. In at least one embodiment, the IC layout diagram is generated by an EDA tool, such as an APR tool. The APR tool receives the design of the IC in the form 55 of a netlist as described herein. The APR tool performs floor planning to identify circuit elements, which are to be electrically connected to each other and which are to be placed in close proximity to each other, for reducing the area of the IC and/or reducing time delays of signals travelling over the 60 interconnections or nets connecting the electrically connected circuit elements. In some embodiments, the APR tool performs partitioning to divide the design of the IC into a plurality of blocks or groups, such as clock and logic groups. Example operations by the APR tool include, but are not 65 limited to, a cell placement operation and a routing opera4

In a cell placement operation, the APR tool performs cell placement. Cells configured to provide pre-defined functions and having pre-designed layout diagrams are stored in one or more cell libraries, for example, in Library Exchange Format (LEF). LEF is a specification that includes design rules and information about cells in a library. In at least one embodiment, LEF is used with DEF to represent a physical layout of an IC being designed. The APR tool accesses various cells from one or more cell libraries, and places the cells in an abutting manner to generate an IC layout diagram corresponding to the IC schematic. Each cell includes one or more circuit elements and/or one or more nets. A circuit element is an active element or a passive element. Examples of active elements include, but are not limited to, transistors and diodes. Examples of transistors include, but are not limited to, metal oxide semiconductor field effect transistors (MOSFET), complementary metal oxide semiconductor (CMOS) transistors, bipolar junction transistors (BJT), high voltage transistors, high frequency transistors, p-channel and/or n-channel field effect transistors (PFETs/NFETs) or the like, FinFETs, planar MOS transistors with raised source/drains, or the like. Examples of passive elements include, but are not limited to, capacitors, inductors, fuses, and resistors. Examples of nets include, but are not limited to, vias, conductive pads, conductive traces, and conductive redistribution layers, or the like.

In a routing operation, the APR tool performs routing to route various nets interconnecting the placed circuit elements. The routing is performed to ensure that the routed interconnections or nets satisfy a set of constraints. For example, the routing operation includes global routing, track assignment and detailed routing. During the global routing, routing resources used for interconnections or nets are allocated. For example, the routing area is divided into a number of sub-areas, pins (or terminals) of the placed circuit elements are mapped to the sub-areas, and nets are constructed as sets of sub-areas in which interconnections are physically routable. During the track assignment, the APR tool assigns interconnections or nets to corresponding conductive layers of the IC layout diagram. During the detailed routing, the APR tool routes interconnections or nets in the assigned conductive layers and within the global routing resources. For example, detailed, physical interconnections are generated within the corresponding sets of sub-areas defined at the global routing and in the conductive layers defined at the track assignment. After the routing operation, the APR tool outputs the IC layout diagram including the placed circuit elements and routed nets. The described APR tool is an example. Other arrangements are within the scope of various embodiments. For example, in one or more embodiments, one or more of the described operations are omitted or one or more additional operations are added before, during, or after the described operations.

In some embodiments, one or more verifications are performed after the cell placement and routing operation 120. Example verifications include, but are not limited to, a layout-versus-schematic (LVS) check, and a design rule check (DRC). Other verification processes are usable in other embodiments.

An LVS check is performed to ensure that the generated IC layout diagram corresponds to the design of the IC. Specifically, an LVS checking tool, i.e., an EDA tool, recognizes electrical components as well as connections therebetween from the patterns of the generated IC layout diagram. The LVS checking tool then generates a layout netlist representing the recognized electrical components and connections. The layout netlist generated from the IC

layout diagram is compared, by the LVS checking tool, with the schematic netlist of the design of the IC. If the two netlists match within a matching tolerance, the LVS check is passed. Otherwise, correction is made to at least one of the IC layout diagram or the design of the IC by returning the process to at least one of the IC design generation operation 110 or the cell placement and routing operation 120.

A DRC is performed, e.g., by an EDA tool, to ensure that the IC layout diagram satisfies certain manufacturing design rules, i.e., to ensure manufacturability of the IC. If one or more design rules is/are violated, correction is made to at least one of the IC layout diagram or the design of the IC by returning the process to at least one of the IC design generation operation 110 or the cell placement and routing operation 120. Examples of design rules include, but are not limited to, a width rule which specifies a minimum width of a pattern in the IC layout diagram, a spacing rule which specifies a minimum spacing between adjacent patterns in the IC layout diagram, an area rule which specifies a minimum area of a pattern in the IC layout diagram, etc.

At resistance and capacitance (RC) extraction operation 130, an RC extraction is performed, e.g., by an EDA tool, to determine parasitic parameters, e.g., parasitic resistance and parasitic capacitance, of components in the IC layout diagram for timing simulations in one or more subsequent operations.

At static timing analysis (STA) operation 140, an EDA tool estimates delays in a plurality of paths in the IC layout diagram. Input data for the STA operation 140 include, but are not limited to, the IC layout diagram, the parasitic parameters extracted by the RC extraction operation 130, cell delays obtained from one or more cell libraries having cells included in the IC layout diagram. Output data from the STA operation 140 are included in a timing report described herein. In at least one embodiment, the STA operation 140 is performed without a simulation of operation of an IC corresponding to the IC layout diagram. In at least one embodiment, when the delays estimated in the STA opera- 40 tion 140 for one or more paths fail to meet corresponding timing requirements, correction is made to at least one of the IC layout diagram or the design of the IC by returning the process to at least one of the IC design generation operation 110 or the cell placement and routing operation 120.

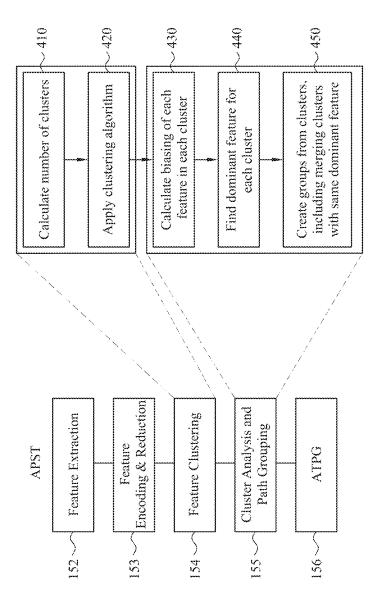

At Automatic Path Selection and Testing (APST) operation 150, the paths in the IC layout diagram are grouped and test patterns are generated for the grouped paths. In some embodiments, the APST operation 150 is performed at least partially by an EDA tool. An exploded schematic view 50 showing further operations of the APST operation 150 in accordance with some embodiments is also illustrated in FIG. 1. Input data for the APST operation 150 include one or more of the IC schematic 113 output from the IC design generation operation 110, the IC layout diagram 123 output from the cell placement and routing operation 120, and the timing report 143 from the STA operation 140. In the example configuration in FIG. 1, the APST operation 150 comprises a feature extraction operation 152, a feature encoding and reduction operation 153, a feature clustering operation 154, a cluster analysis and path grouping operation 155, and an Automatic Test Pattern Generation (ATPG) operation 156.

At the feature extraction operation 152, a plurality of 65 features of the paths in the IC layout diagram is extracted, as described with respect to FIGS. 2A-2G.

6

At the feature encoding and reduction operation 153, the extracted features are encoded and reduced to obtain a reduced set of features, as described with respect to FIGS. 3A-3G.

At the feature clustering operation **154**, the paths of the IC layout diagram are divided into a plurality of clusters, as described with respect to FIG. **4**.

At the cluster analysis and path grouping operation 155, the clusters are analyzed and grouped into a plurality of groups with associated unique dominant features, as described with respect to FIG. 4.

At the ATPG operation **156**, one or more ATPG methods or algorithms are used to generate test patterns for one or more paths in each group, as described herein.

At testing operation 160, a test is performed for one or more paths in each group, using the test patterns generated by the ATPG operation 156 to determine whether the IC layout diagram or an actual IC manufactured in accordance with the IC layout diagram meets a predetermined specification of one or more timing requirements. In at least one embodiment, the test comprises a post-layout simulation, e.g., performed by an EDA tool, to simulate an operation of an IC corresponding to the IC layout diagram. In some embodiments, the test is performed by Automatic Test Equipment (ATE) having hardware structures, such as probes, to electrically couple to an actual IC (chip) fabricated in accordance with the IC layout diagram, for testing operation of the actual IC. In one or more embodiments, the test at the testing operation 160 comprises both a post-layout simulation by an EDA tool and a test performed by ATE on an actual IC. When the IC layout diagram and/or an actual IC fabricated based on the IC layout diagram pass the test, additional verification processes are performed, or ICs are fabricated based on the IC layout diagram.

At modification operation 170, correction is made when the IC layout diagram and/or an actual IC fabricated based on the IC layout diagram fail the test at the testing operation 160. In some embodiments, correction is made to at least one of the IC layout diagram or the design of the IC by returning the process to at least one of the IC design generation operation 110 or the cell placement and routing operation 120. The correction to the design of the IC at the IC design generation operation 110 results in corresponding correction to the IC layout diagram at the cell placement and routing operation 120. In some embodiments, correction is made to one or more cell libraries having cells included in the IC layout diagram. The correction to the one or more cell libraries results in corresponding correction to the IC layout diagram at the cell placement and routing operation 120. In some embodiments, correction is made to a manufacturing process for manufacturing an IC corresponding to the IC layout diagram. The IC design flow 100 in FIG. 1 is an example. In some embodiments, the IC design flow 100 includes one or more further operations, and/or one or more of the described operations are omitted.

FIGS. 2A-2F are schematic logic diagrams of various sections of an IC layout diagram with example paths, in accordance with some embodiments. FIG. 2G is a schematic view showing various extracted features of paths in an IC layout diagram, in accordance with some embodiments.

FIG. 2A is a schematic logic diagrams of a section 200A of an IC layout diagram, with path 1 in accordance with some embodiments. The section 200A comprises a plurality of logic gates 201-204, and a plurality of nets (or wires) 205-210 which couple logic gates 201-204 with each other and with two flip-flops FF1, FF2. For simplicity, each logic gate is assumed to be a cell. Path 1 comprises net 205, cell

201, net 206, cell 204 and net 207 coupled serially between flip-flops FF1, FF2. In at least one embodiment, path 1 is identified in the timing report 143 output from the STA operation 140. Features of path 1 include features of nets 205, 206, 207 and features of cells 201, 204 in path 1.

Example features of a net include, but are not limited to, "physical net length in metal layer," "total physical net length," "number of vias in wire (or net)," "net delay," "slew-ratio," "layout shape," or the like. The feature "physical net length in metal layer" indicates a physical length of 10 a section of the net arranged in a metal layer, such as M0, M1, M2 or the like. The feature "total physical net length" indicates a total physical length of the net in all metal layers in which the net is arranged. The feature "number of vias in wire (or net)" indicates a number of vias that couple different 15 segments of the net in different metal layers together. The feature "net delay" indicates a time delay of a signal travelling through the net due to the parasitic capacitance and parasitic resistance of the net. The feature "slew-ratio" indicates how fast or slow a leading edge or a trailing edge 20 of a signal rises or falls. The feature "layout shape" indicates a shape of the net. Example shapes of a net include, but are not limited to, L-shape, I-shape, T-shape, or the like. Other features of a net are within the scopes of various embodi-

Example features of a cell include, but are not limited to, "driving strength," "VT type," "number of inputs," "number of outputs," "function type," "number of transistors," "height," "pitch," "layout shape," "sensitivity delay" or the like. The feature "driving strength" indicates a designed load 30 of the cell. The feature "VT type" indicates a type of threshold voltage (VT) at which transistors in the cell are turned ON or OFF. Example VT types include, but are not limited to, high threshold voltage (HVT), low threshold voltage (LVT), ultralow threshold voltage (ULVT), standard 35 threshold voltage (SVT). Generally, cells with lower threshold voltages are faster but consume more power than cells with higher threshold voltages. The feature "number of inputs" indicates the number of inputs of the cell. The feature "number of outputs" indicates the number of outputs 40 of the cell. The feature "function type" indicates a logic type of the cell. Example logic types include, but are not limited to, AOI (AND-OR-Invert), AND, XOR, OR, NAND, NOR, INV (Invert) or the like. The feature "number of transistors" indicates the number of transistors in the cell. The feature 45 "height" indicates a height of the cell in a direction along gate regions of transistors in the cell. The feature "pitch" indicates a pitch between adjacent gate regions. The feature "layout shape" indicates a shape of a net inside the cell. The feature "sensitivity delay" indicates a time delay of a signal 50 travelling through the cell. Other features of a cell are within the scopes of various embodiments. Further example features of paths are described with respect to FIG. 2G.

FIG. 2B is a schematic logic diagrams of a section 200B of an IC layout diagram, with path 2 in accordance with 55 some embodiments. In the example configuration in FIG. 2B, nets 211-214 along path 2 have physical net lengths in metal layer M3 being 50 units, 30 units, 100 units and 200 units, respectively. The physical net lengths of nets 211-214 in metal layer M3 are greater than in other metal layers. In 60 other words, nets 211-214 along path 2 are dominantly arranged in metal layer M3, or path 2 is dominated by nets in metal layer M3. Because nets 211-214 are dominantly arranged in metal layer M3, path 2 will be affected more by a variation in metal layer M3 compared to other paths not 65 dominated by metal layer M3. When there is a variation in metal layer M3, small delays along nets 211-214 in path 2

8

will accumulate into a larger, easier to detect delay. In some embodiments as described herein, by grouping paths based on a dominant feature, such as metal layer M3 for path 2 or another feature described with respect to FIGS. 2C-2G, and testing the grouped paths, it is possible to identify and fix small delay defects (SDDs).

FIG. 2C is a schematic logic diagrams of a section 200C of an IC layout diagram, with path 3 in accordance with some embodiments. In the example configuration in FIG. 2C, cells 215-218 are arranged along path 3. Cells 215, 216, 218 are configured from transistors having a low threshold voltage (LVT), and cell 217 is configured from transistors having a standard threshold voltage (SVT). In other words, the cells along path 3 are dominantly configured as LVT cells, or path 3 is dominated by LVT cells.

FIG. 2D is a schematic logic diagrams of a section 200D of an IC layout diagram, with path 4 in accordance with some embodiments. In the example configuration in FIG. 2D, cells 219-221 are arranged along path 4. Each of cells 219-221 is configured to have three inputs. In other words, the cells along path 4 are dominantly configured as 3-input cells, or path 4 is dominated by 3-input cells.

FIG. 2E is a schematic logic diagrams of a section 200E of an IC layout diagram, with path 5 in accordance with some embodiments. In the example configuration in FIG. 2E, nets 222-226 are arranged along path 5. The numbers of vias in nets 222-226 are 5, 59, 137, 8, and 23, respectively. The total number of vias in the nets of path 5 is greater than an average total number of vias in the plurality of paths of the IC layout diagram. In other words, path 5 is dominated by the number of vias in the path.

FIG. 2F is a schematic logic diagrams of a section 200F of an IC layout diagram, with path 6 in accordance with some embodiments. In the example configuration in FIG. 2F, nets 227-230 arranged along path 6 have physical net lengths in metal layer M5 being 121.3, 68.5, 259.4 and 97.6, respectively. The total physical net lengths of the nets of path 6 in metal layer M5 is greater than other paths. In other words, path 6 is dominated by the physical net length in metal layer M5.

FIG. 2G is a schematic view of a feature list 200G showing various extracted features of paths in an IC layout diagram, in accordance with some embodiments. The feature list 200G is an example of a result of the feature extraction operation 152. The feature list 200G comprises one or more of timing features 240, logical features 250, and physical features 260. The feature list 200G is not exhaustive, and other features are within the scopes of various embodiments.

One or more of the timing features 240 are obtained as a result of the STA operation 140, included in the timing report 143 supplied to the APST operation 150, and then extracted from the timing report 143 by the feature extraction operation 152. An example feature is slack 241. Slack of a path is an amount of delay tolerable in a path before a timing constraint is violated. A negative value of slack indicates that the path already violates the timing constraint. A zero value of slack indicates that an IC corresponding to the IC layout diagram is operable, but no timing margin is available. A positive value of slack indicates that the IC is operable with a timing margin. An IC design flow attempts to achieve positive, or at least non-negative, values of slack in all paths.

One or more of the timing features 240 are obtained from a library. An example is library setup/hold time 242. The library setup/hold time 242 is a predetermined or known timing parameter of a cell and is retrieved from a library corresponding to the cell. In at least one embodiment, the

library setup/hold time 242 is extracted from the library in the feature extraction operation 152. In one or more embodiments, the library setup/hold time 242 is included, at the STA operation 140, into the timing report 143, and then sent to the APST operation 150 for extraction in the feature 5 extraction operation 152.

One or more of the logical features 250 are extracted from the IC schematic 113, e.g., a Verilog netlist.

One or more of the physical features **260** are extracted from the IC layout diagram **123**, e.g., from one or more DEF 10 and/or LEF files containing the IC layout diagram **123**.

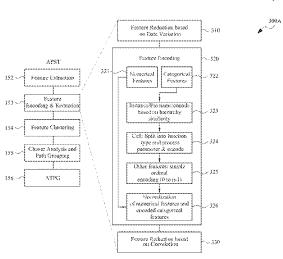

FIG. 3A is a flow chart of a process 300A in the feature encoding and reduction operation 153, in accordance with some embodiments. The process 300A comprises a first feature reduction operation 310, a feature encoding operation 320, and a second feature reduction operation 330.

At the first feature reduction operation 310, one or more features among the plurality of features extracted by the feature extraction operation 152 are removed based on data variation of the features across the plurality of paths of the 20 IC layout diagram. The first feature reduction operation 310 is described herein with respect to FIG. 3B. In at least one embodiment, the first feature reduction operation 310 is omitted.

At the beginning of the feature encoding operation 320, 25 the features remaining after the first feature reduction operation 310 are divided into numerical features 321 and categorical features 322. A numerical feature is a feature having numerical values. A categorical feature is a feature having non-numerical values. Example non-numerical values 30 include, but are not limited to, strings of characters. Example of numerical features and categorical features are described herein in with respect to FIG. 3C. Because numerical values of the numerical features 321 are ready for further calculations, the numerical features 321 are not subjected to one or 35 more of first-third encoding operations 323-325. To the contrary, non-numerical values of the categorical features 322 are not ready for further calculations, and are converted or encoded to obtain corresponding converted numerical values in one or more of the first through third encoding 40 operations 323-325 in the feature encoding operation 320.

At the first encoding operation 323, a non-numerical value corresponding to a name of a pin or an instance (e.g., from a netlist) is encoded or converted into a corresponding converted numerical value, based on one or more hierarchy 45 levels associated with the pin or instance, as described with respect to FIG. 3C.

At the second encoding operation **324**, a non-numerical value corresponding to features of a cell is split into a function type and a process parameter, and encoded or 50 converted into corresponding converted numerical values, as described with respect to FIG. **3**D.

At the third encoding operation 325, a non-numerical value corresponding to a further feature is encoded or converted into a corresponding converted numerical value, 55 using ordinal encoding, as described with respect to FIG. 3E.

At a normalization operation **326** of the feature encoding operation **320**, the numerical values of the numerical features and the converted numerical values of the categorical features are normalized, as described with respect to FIG. 60 **3**F. The described operations in the feature encoding operation **320** are example. Other arrangements for converting non-numerical values to converted numerical values are within the scopes of various embodiments.

At the second feature reduction operation **330**, based on 65 the normalized values output from the normalization operation **326**, one or more features are further removed based on

10

correlation with slack, as described with respect to FIG. 3G. As a result, a reduced set of features is obtained, as described with respect to FIG. 3H.

FIG. 3B is a schematic data representation 300B of example features in the first feature reduction operation 310, in accordance with some embodiments. For simplicity, schematic data representations of a limited number of example features "slack," "clock uncertainty," "LVT cells," "net length" and "net area" are illustrated in FIG. 3B, in the form of corresponding graphs 311-315. The abscissa of each graph 311-315 indicates the number N of paths in the plurality of paths of the IC layout diagram. The ordinate of each graph 311-315 indicates a value of the corresponding feature for each of the N paths. The data presentations are for illustrative purposes, and are omitted in one or more embodiments.

In some embodiments, all features extracted by the feature extraction operation 152 are analyzed to determine variations of the features across the plurality of paths of the IC layout diagram. Features that show no variation across the N paths are removed from further analysis. For example, as shown at graph 312, the value of "clock uncertainty" remains unchanged across the N paths of the IC layout diagram. As a result, "clock uncertainty" is removed from further analysis. Other example features "slack," "LVT cells," "net length" and "net area" have values that vary across the N paths, and are maintained for further analysis. In at least one embodiment, features with incomplete information are also removed from further analysis.

In at least one embodiment, the described removal of one or more features based on data variation and/or information incompleteness is a simple way to reduce the number of features subject to further analysis, thereby reducing the calculation workload.

FIG. 3C is a schematic view of a table 300C including various numerical features 340 and categorical features 345 with corresponding values in several example paths Path #1 through Path\_#4 among the N paths of the IC layout diagram, in accordance with some embodiments. The numerical features 340 include numerical features 341-344 which are timing features corresponding to one or more of the timing features 240 described with respect to FIG. 2G. As shown in FIG. 3C, the numerical features 341-344 have numerical values for each of Path\_#1 through Path\_#4. In this example, the numerical values of the numerical features 341-344 are delay times. The categorical features 345 include categorical features 346-348 which are logical features corresponding to one or more of the logical features 250 described with respect to FIG. 2G. As shown in FIG. 3C, the categorical features 346-348 have non-numerical values which are presented in the form of strings of characters. In this example, the strings of characters of the categorical features 346-348 indicate pin or instance names, cell features, and clock, respectively. The list of features shown in FIG. 3C is an example and is not exhaustive.

Non-numerical values of the categorical feature 346 are shown in more detail in the enlarged view in FIG. 3C, to provide an example of pin or instance name encoding in the first encoding operation 323. Each non-numerical value of the categorical feature 346 indicates a name of a pin or an instance in a corresponding one of Path\_#1 through Path\_#4. Each pin or instance name is presented in the form of a string of characters which includes one or more slash characters "/" to indicate a plurality of hierarchy levels associated with the pin or instance. In the example configuration in FIG. 3C, there are nine hierarchy levels 349-357 in each of the non-numerical values of the categorical feature

and 25

346. The hierarchy level 349 is the highest level, followed by the level 350, and so on, down to the lowest level 357. The string segment in each of the hierarchy levels 349-357 is encoded to be a number, in accordance with a predetermined encoding scheme. For example, the string segment "u12\_logic" at the hierarchy level 355 is encoded to a number "1" for all Path\_#1 through Path\_#4. Similarly, the string segment at each of the hierarchy levels 349-354 is encoded to a number "1" for all Path\_#1 through Path\_#4. At the hierarchy levels 356, 357, the string segments in the 10 Path #1 through Path #4 are different and, therefore, are encoded to different numbers. Specifically, at the hierarchy level 356, the string segment "ucpu3\_arb" is the same in Path\_#1 and Path\_#2 and is encoded to "21" in Path\_#1 and Path\_#2, whereas the string segment "uarb\_1c" is the same 15 in Path\_#3 and Path\_#4 and is encoded to "10" in Path\_#3 and Path\_#4. At the hierarchy level 357, the string segment is the same in Path\_#1 and Path\_#2 and is encoded to "60" in Path #1 and Path #2, whereas different string segments in Path #3 and Path #4 are encoded to "40" and "50." 20 respectively. As a result of the described pin or instance name encoding operation 323, the non-numerical values of the categorical feature 346 for Path\_#1 through Path\_#4 are

encoded to corresponding converted numerical values

"11111112160," "11111112160," "111111111040,"

"11111111050," respectively, as also illustrated in FIG. 3F. FIG. 3D is a schematic view of a table 300D including the categorical feature 347 with corresponding non-numerical values being encoded in the second encoding operation 324, in accordance with some embodiments. The categorical 30 feature 347 includes several features of a cell, and is split into further categorical features 360, 361 indicating a cell function type and a process parameter of the cell, respectively. Each non-numerical value or a string of characters of the categorical feature 347 is also split into shorter segments 35 corresponding to the categorical features 360, 361. For example, the non-numerical value or a string of characters "DFRPQD4BWP300H8P63PDULVT" of the categorical feature 347 is split into a string segment 362 "DFRPQ," a string segment 363 "D4," a string segment 364 40 "BWP300H8P63PD," and a string segment 365 "ULVT." The string segment 362 "DFRPQ" indicates the cell function type being a flip-flop, and is converted to a non-numerical value 366 "Flop" of the categorical feature 360. The string segment 363 "D4" indicates the driving strength of the cell. 45 In the example in FIG. 3D, the driving strength is not shown further for simplicity. However, it is within the scopes of one or more embodiments to include this feature in further analysis. The string segment 364 "BWP300H8P63PD" indicates the process parameter, and is converted to a non- 50 numerical value 367 "BWP300H8P63P" of the categorical feature 361. The string segment 365 "ULVT" indicates the threshold voltage of the cell. In the example in FIG. 3D, the threshold voltage is not shown further for simplicity. However, it is within the scopes of one or more embodiments to 55 include this feature in further analysis. Similarly, to the first encoding operation 323, each of the non-numerical values **366**, **367** is encoded to be a number, in accordance with a predetermined encoding scheme. For example, the nonnumerical value 366 "Flop" is encoded to a corresponding 60 converted numerical value 368 "1," and the non-numerical value 367 "BWP300H8P63P" is encoded to a corresponding converted numerical value 369 "1." The other non-numerical values, collectively indicated in FIG. 3D at 370, of the categorical feature 347 are similarly split and encoded to corresponding converted numerical values, collectively indicated in FIG. 3D at 371.

12

FIG. 3E is a schematic view of a table 300E including the categorical feature 348 with corresponding non-numerical values being encoded in the third encoding operation 325, in accordance with some embodiments. Similarly, to the first encoding operation 323, each of the non-numerical values of the categorical feature 348 is encoded to be a number, in accordance with a predetermined encoding scheme, e.g., an ordinal encoding. For example, the non-numerical value "CA72\_ACLK" is encoded to a corresponding converted numerical value "1." The other non-numerical values of the categorical feature 348 are similarly encoded, as indicated in FIG. 3E.

FIG. 3F is a schematic view of a table 300F including various numerical features 340 and categorical features 345 with corresponding numerical and converted numerical values in the normalization operation 326, in accordance with some embodiments. The table 300F includes numerical values of the numerical features 340, collectively indicated in FIG. 3F at 372, and converted numerical values of the categorical features 345, collectively indicated in FIG. 3F at 373. The numerical values 372 of the numerical features 340 are the same as corresponding numerical values in the table 300C. The converted numerical values 373 of the categorical features 345 are obtained by encoding or converting the corresponding non-numerical values of the categorical features 345 in the first-third encoding operations 323-325, as described with respect to FIGS. 3C-3E. The numerical and converted numerical values 372, 373 are normalized to obtain corresponding normalized values 380. For example, the numerical values "0.000228," "0.007996," "0.005491" and "0.006957" of the numerical feature 341 (hereinafter feature LIB) are normalized to obtain corresponding normalized values "0.01502," "0.08514," "0.04104" "0.05694."

As a result of the normalization operation 326, each feature has a plurality of normalized values corresponding to N paths of the IC layout diagram. For example, feature LIB has normalized values "0.01502," "0.08514," "0.04104" and "0.05694" for Path #1 through Path #4. Likewise, the feature slack also has normalized values (not shown) for Path\_#1 through Path\_#4. These two sets of normalized values for the features LIB and slack are used to determine a correlation coefficient between the features LIB and slack in the second feature reduction operation 330. In at least one embodiment, a reason why slack is chosen to be the base feature for determining correlation with the other features is because testing is done for timing verification and/or because the STA operation 140 in one or more embodiments is configured for slack optimization. Base features, other than slack, for determining correlation are within the scopes of various embodiments.

In some embodiments, the following formula (1) is used to calculate a correlation coefficient

$$r_{xy} = \frac{\sum_{k=1}^{N} (x_i - \overline{x})(y_i - \overline{y})}{\sqrt{\sum_{k=1}^{N} (x_i - \overline{x})^2} \sqrt{\sum_{k=1}^{N} (y_i - \overline{y})^2}}$$

(1)

where  $r_{xy}$  is the correlation coefficient,  $x_i$  is the normalized value of slack at the i-th path among the N paths of the IC layout diagram,  $y_i$  is the normalized value of another feature, e.g., LIB, at the i-th path,  $\overline{x}$  is the mean of all normalized values of slack across all N paths, and  $\overline{y}$  is the mean of all normalized values of LIB across all N paths. The correlation

coefficients between slack and other features are similarly calculated, and example results are given in FIG. 3G.

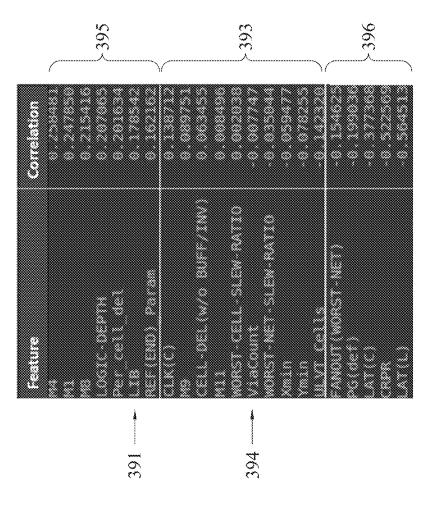

FIG. 3G is a schematic view of a table 300G including various features with corresponding correlation coefficients in the second feature reduction operation 330, in accordance with some embodiments. As illustrated at 391, the correlation coefficient calculated as described herein between LIB and slack across N paths of the IC layout diagram is "0.178542" in this example. In the table 300G, the correlation coefficients are sorted in the descending order.

Features corresponding to the correlation coefficients within a predetermined range 393 are removed from further analysis. In some embodiments, the predetermined range is between -0.15 and 0.15. Features with the correlation coefficients in this predetermined range around zero are considered to have little or no correlation with slack. When there is a variation in such a feature, e.g., ViaCount (the number of vias in a path) as indicated at 394, slack will be unlikely affected due to the little or no correlation between ViaCount and slack. In other words, in this specific example, ViaCount 20 due to its low correlation with slack is considered to have little or no significant effect on slack and timing performance. The feature ViaCount is therefore removed from further analysis. In at least one embodiment, this removal reduces the calculation workload at further, subsequent 25 analysis. Other predetermined ranges for removing features considered to have little or no correlation with slack are within the scopes of various embodiments.

Features corresponding to the correlation coefficients outside the predetermined range 393 are retained for further 30 analysis. For example, features corresponding to the correlation coefficients in ranges 395 and 396 respectively above and below the predetermined range 393 are retained for further analysis. Features corresponding to the correlation coefficients in the range 395 have positive correlation with 35 slack, which means when a value of one of these features is increased, there is a likelihood that slack is also increased. Features corresponding to the correlation coefficients in the range 396 have negative correlation with slack, which there is a likelihood that slack is decreased. Due to the sufficient correlation with slack, the features corresponding to the correlation coefficients in the ranges 395, 396 are considered to have potential effect on slack and timing performance. These features are retained for further analysis, and together constitute a reduced set of features an example of which is given in FIG. 3H.

FIG. 3H is a schematic view showing a reduced set 300H of features of paths in an IC layout diagram, in accordance with some embodiments. The reduced set 300H lists all extracted features as in the feature list 200G in FIG. 2G. However, features that have been removed by the first feature reduction operation 310 based on data variation and the second feature reduction operation 330 based on correlation with slack are indicated as being stricken through in 55 the reduced set 300H. The reduced set 300H is an example result of the feature encoding and reduction operation 153. In at least one embodiment, the encoding processing in the feature encoding and reduction operation 153 makes it possible to analyze categorical features in a manner similar to numerical features as described herein. In at least one embodiment, the feature reduction in the feature encoding and reduction operation 153 makes it possible to remove features that are unlikely to affect timing performance and to reduce calculation workload.

FIG. 4 is a flow chart of a process 400 in the feature clustering operation 154 and cluster analysis and path group14

ing operation 155, in accordance with some embodiments. The feature clustering operation 154 comprises operations 410, 420 with which the paths of the IC layout diagram are clustered or divided into a plurality of clusters. The cluster analysis and path grouping operation 155 comprises operations 430, 440, 450 with which the clusters are analyzed and grouped into a plurality of groups with associated unique dominant features.

At operation 410, a number of clusters into which the N paths of the IC layout diagram are to be divided is determined. In some embodiments, the following formula (2) is used to calculate the number k of clusters:

$$k = \sqrt[2]{N/2} \tag{2}$$

At operation 420, a clustering algorithm is applied for clustering the N paths. In some embodiments, the clustering algorithm applied in operation 420 is K-means clustering. K-means clustering is used in unsupervised learning. Other clustering algorithms are within the scopes of various embodiments.

Data for K-means clustering include the reduced set 300H of m features obtained as a result of the feature encoding and reduction operation 153, and the normalized values of the m features in the N paths obtained as a result of the normalization operation 326. Each path is presented as a data point including m normalized values of the m features. The objective of K-means clustering is to cluster the N data points into k clusters  $S_1 cdots S_k$  in an iterative process to achieve the following minimization:

$$\arg\min_{S} \sum_{i=1}^{k} \frac{1}{2|S_{i}|} \sum_{x, y \in S_{i}} ||x - y||^{2}$$

(3)

At operation 430, a biasing of each of the m features is means when a value of one of these features is increased, 40 calculated in each of the k clusters, for example, using the following formula:

$$CB_{nx} = (CM_{nx} - DS_x)/DS_x \tag{4}$$

where  $CB_{nx}$  is a biasing of feature x in cluster n,  $CM_{nx}$  is 45 a mean value of feature x in the paths in cluster n, and  $DS_x$ is a mean value of feature x in all N paths.

At operation 440, based on the biasing of each feature in each cluster calculated at operation 430, a dominant feature is determined for each cluster. For example, for each cluster n, when  $(CB_{nx}/\Sigma_{i=1}^{m}CB_{n}i)$  is greater than a predetermined threshold X, cluster n is biased toward feature x, and feature x is determined as the dominant feature of cluster n. In some embodiments, the threshold X for determining whether cluster n is biased toward feature x is a value from 40% to 60%. Any other values of the threshold X are within the scopes of various embodiments. For example, in one or more embodiments, the threshold X is 70%, 85%, or 90%. In at least one embodiment with the threshold X being greater than 50%, there is a maximum of one feature satisfying the condition  $(CB_{nx}/\Sigma_{i=1}{}^{m}CB_{n}i)>X$  in a cluster. In at least one embodiment with the threshold X being 50% or lower, there is a potential situation where more than one features satisfy the condition  $(CB_{nx}/\Sigma_{i=1}{}^{m}CB_{n}i)>X$  in a cluster. In such a situation, the cluster is determined to be dominated by more than one features.

When no cluster has  $(CB_{nx}/\Sigma_{i=1}{}^{m}CB_{n}i)$  greater than the predetermined threshold X for feature x, the cluster with the

greatest  $(CB_m/\Sigma_{i=1}{}^mCB_ni)$  is determined to have feature x as the dominant feature. This determination is applicable even when the cluster with the greatest  $(CB_m/\Sigma_{i=1}{}^mCB_ni)$  is already determined to have a dominant feature other than feature x. It is within the scope of one or more embodiments that a cluster has more than one dominant features. It is also within the scope of one or more embodiments that a feature is determined to be a dominant feature of more than one

As a result of the operation 440, each of the k clusters has at least one dominant feature being one of the m features, and each of the m features is determined as a dominant feature of at least one of the k clusters.

At operation 450, m groups of paths are created from the 15 k clusters, so that each group has a unique dominant feature that is different from dominant features of the other groups. For example, when, among the k clusters, a first feature has been determined to be the dominant feature of only one cluster, then that cluster is designated as the group having 20 the first feature as the dominant feature. Further, when, among the k clusters, a second feature has been determined to be the dominant feature of more than one clusters, such clusters are merged together into the group having the second feature as the dominant feature. In some embodi- 25 ments, each path is included in one group, resulting in a plurality of non-overlapping groups. In a further example, where a cluster has been determined to have several dominant features, the cluster is merged into several groups corresponding to the several dominant features. As a result, at least one embodiment includes a potential situation in which a path is included in more than one groups.

In some embodiments, as a result of the operation **450** of the cluster analysis and path grouping operation **155**, the N paths of the IC layout diagram are grouped into m groups with m different dominant features each corresponding to one of the m features in the reduced set **300**H of features obtained by the feature encoding and reduction operation **153**. A dominant feature of a group is a feature by which the paths in the group are dominated, as described with respect to FIGS. **2B-2F**. For example, the paths in a group having metal layer M**3** as the dominant feature are dominated by metal layer M**3**, as described with respect to FIG. **2B**.

As can be seen in FIG. **4**, after the operation **450** of the 45 cluster analysis and path grouping operation **155**, the process proceeds to the ATPG operation **156** where one or more ATPG methods or algorithms are used to generate test patterns for one or more paths in each group for which a dominant feature has been designated. A specific example is 50 described herein for a group having metal layer M**3** as the dominant feature.

Specifically, the paths in the group having metal layer M3 as the dominant feature are identified in a report, e.g., a netlist, from the cluster analysis and path grouping operation 55 155 to the ATPG operation 156 for subsequent testing. In practice, not all paths in the group are testable, due the large number of paths or a specific nature of a path that renders the path untestable. For all testable paths in the group, the ATPG operation 156 generates corresponding test patterns. The 60 generated test patterns vary from path to path depending on, for example, the types and/or number of cells or gates on the path, the test strategy, or the ATPG method or algorithm used to generate the test pattern. An example ATPG strategy used in one or more embodiments is path delay ATPG which is 65 used to generate both robust and non-robust path delay test patterns. As described herein with respect to FIG. 1, the

16

generated test patterns are used in a simulation for IC design verification before fabrication, and/or in an ATE for testing an actual, fabricated IC.

When one of the paths fails the test, because the failed path was identified by the APST operation 150 as belonging to a group with the dominant feature being metal layer M3, it is possible in one or more embodiments to select a correction strategy related to the dominant feature, i.e., metal layer M3, to fix or improve timing performance of the failed path. Such correction strategy related to metal layer M3 is expected in at least one embodiment to also improve performance of other paths in the same group dominated by metal layer M3. As a result, it is possible in some embodiments to target or improve multiple paths with a single correction strategy, thereby saving time and efforts in the IC design and/or fabrication process. The above advantage is achievable not only at a simulation before signing-off for fabrication or when testing an actual, fabricated IC, but also at an earlier stage. For example, in at least one embodiment, identified groups of paths with designated dominant features are relied on to define a strategy for fixing timing issues discovered by the STA operation 140.

There are several approaches for fixing or improving a failed path based on the identified dominant feature of the path. In the example with metal layer M3 being the dominant feature, a strategy in accordance with some embodiments is to reroute at least a portion of the failed path in a different metal layer. A further strategy is to tune a manufacturing process to improve formation of interconnects in metal layer M3 and/or other metal layers around metal layer M3. Other correction strategies are within the scopes of various embodiments. The described advantages are not limited to the specific example with metal layer M3 as the dominant feature. Similar advantages are obtainable in one or more embodiments with respect to paths and groups having other dominant features, as described with respect to FIG. 2G or 3H.

Compared to other approaches, it is possible in some embodiments to identify a larger number of paths to be tested, thereby increasing the likelihood of locating and correcting small delay defects (SDDs) while covering a wide range of potential causes for SDDs. As described herein, SDDs involve small delay variations due to various factors including, but not limited to, fabrication process variations, power supply noise, crosstalk, or the like. In some situations, although delays at individual cells or nets are small and within specifications, the cumulative delay of multiple such small delays, especially over a long path, is potentially large enough to cause failure. In order to detect a potential SDD failure, other approaches select and test top critical paths, i.e., longest paths and/or paths with smallest slack based on an STA timing report. Such an approach focuses on a narrow range of issues and potentially results in a small number of paths selected for testing and/or being tested, without providing sufficient coverages for various causes for SDDs.

In contrast, in one or more embodiments, because the paths identified for testing are directed to a wide range of features, as described with respect to FIGS. **2**G and **3**H, a larger number of paths end up being tested, while covering various potential causes for SDDs. At the same time, critical paths covered by the other approaches are still covered in one or more embodiments which include one or more groups of paths with dominant features being timing features, including slack.

The wide coverage for potential causes for SDDs in at least one embodiment makes it possible to locate and fix various systematic defects which are one of the major

challenges in advanced process nodes. Other approaches lack this capability. In some embodiments, further advantages include, but are not limited to, distributed process defect coverage for SDDs, ability to target any specific feature and/or process issue, independence of process nodes.

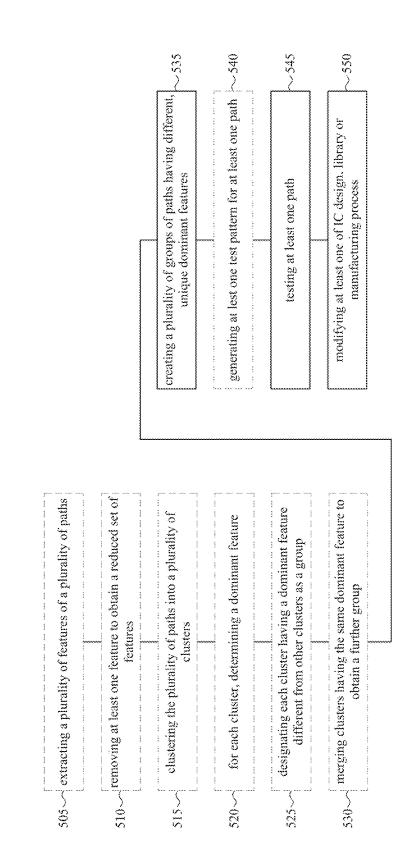

FIG. 5 is a flow chart of a method 500, in accordance with some embodiments. In at least one embodiment, method 500 is performed in whole or in part by a processor as described herein.

At operation **505**, a plurality of features of a plurality of 10 paths in an integrated circuit (IC) layout diagram is extracted. For example, features are extracted from at least one of a Verilog netlist containing an IC schematic corresponding to the IC layout diagram, one or more DEF and/or LEF files containing the IC layout diagram, a timing report 15 of an STA, or a library, as described with respect to FIG. **2**G.

At operation 510, at least one feature is removed from the plurality of features to obtain a reduced set of features, based on a correlation coefficient of the at least one feature with slack across the plurality of paths and/or based on the at least 20 one feature having no variation. For example, a correlation coefficient of each feature with slack across the plurality of paths is calculated, as described with respect to FIG. 3G. In response to the correlation coefficients of one or more features being within a predetermined range, the one or more 25 features are removed from the plurality of features, resulting in a reduced set of features, as described with respect to FIG. 3H. In at least one embodiment, operation 510 is omitted, for example, when all features have variations and the correlation coefficients of all features with slack across the plurality 30 of paths are outside the predetermined range described with respect to FIG. 3G.

At operation **515**, the plurality of paths is clustered into a plurality of clusters. For example, a clustering algorithm is applied to divide the plurality of paths into a plurality of 35 clusters, as described with respect to the feature clustering operation **154** in FIG. **4**.

At operation **520**, a feature included in the reduced set of features is determined as a dominant feature for each cluster among the plurality of clusters. For example, a dominant 40 feature is determined for each cluster, as described with respect to FIG. **4**. A dominant feature is a feature by which paths in the cluster are dominated, for example, as described with respect to FIGS. **2B-2F**.

At operation **525**, each cluster having the dominant feature different from dominant features of other clusters is designated as a group of paths among a plurality of groups of paths to be created from the plurality of clusters, for example, as described with respect to the operation **450** in FIG. **4**.

At operation **530**, clusters having the same dominant feature are merged to obtain a further group among the plurality of groups, for example, as described with respect to the operation **450** in FIG. **4**.

At operation **535**, the plurality of groups of paths is 55 created from the plurality of paths in the IC layout diagram, where each group has a dominant feature among the plurality of features of the plurality of paths, and the dominant features of the plurality of groups are different from each other, for example, as a result of operations **525**, **530**.

At operation **540**, at least one test pattern is generated for at least one path in each group among the plurality of groups. For example, automatic test pattern generation (ATPG) is performed to generate at least one test pattern, as described with respect to the ATPG operation **156** in FIG. **4**.

At operation 545, at least one path in a group among the plurality of groups is tested. For example, the at least one

18

path is tested by using the generated at least one test pattern in a simulation or by an ATE, as described with respect to the testing operation 160 in FIG. 1.

At operation 550, in response to the testing indicating that the at least one path fails, a modification is made to at least one of the IC layout diagram, at least a portion of at least one library having cells included in the IC layout diagram, or a manufacturing process for manufacturing an IC corresponding to the IC layout diagram. For example, one or more corrections are made to at least one of the IC design, a library or a manufacturing process when a path failed, as described with respect to the modification operation 170 in FIG. 1

In at least one embodiment, all operations 505-550 are automatically performed without user input or intervention.

The described methods include example operations, but they are not necessarily required to be performed in the order shown. Operations may be added, replaced, changed order, and/or eliminated as appropriate, in accordance with the spirit and scope of embodiments of the disclosure. Embodiments that combine different features and/or different embodiments are within the scope of the disclosure and will be apparent to those of ordinary skill in the art after reviewing this disclosure.

In some embodiments, at least one method(s) discussed above is performed in whole or in part by at least one EDA system. In some embodiments, an EDA system is usable as part of a design house of an IC manufacturing system discussed below.

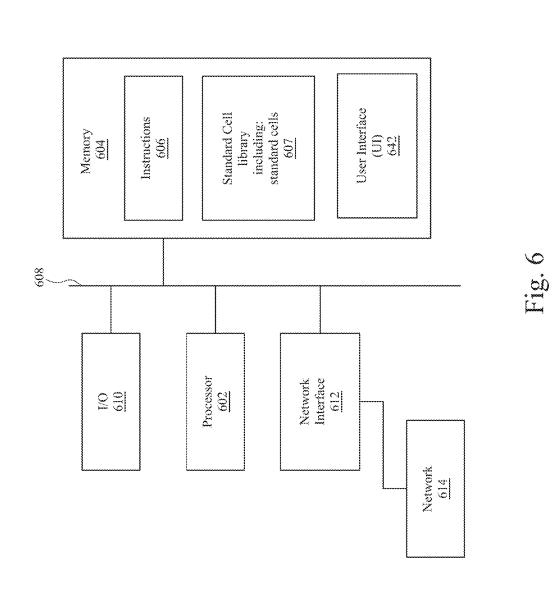

FIG. 6 is a block diagram of an electronic design automation (EDA) system 600 in accordance with some embodiments.

In some embodiments, EDA system 600 includes an APR system. Methods described herein of designing layout diagrams represent wire routing arrangements, in accordance with one or more embodiments, are implementable, for example, using EDA system 600, in accordance with some embodiments.

In some embodiments, EDA system 600 is a general purpose computing device including a hardware processor 602 and a non-transitory, computer-readable storage medium 604. Storage medium 604, amongst other things, is encoded with, i.e., stores, computer program code 606, i.e., a set of executable instructions. Execution of instructions 606 by hardware processor 602 represents (at least in part) an EDA tool which implements a portion or all of the methods described herein in accordance with one or more embodiments (hereinafter, the noted processes and/or methods).

Processor 602 is electrically coupled to computer-readable storage medium 604 via a bus 608. Processor 602 is also electrically coupled to an I/O interface 610 by bus 608. A network interface 612 is also electrically connected to processor 602 via bus 608. Network interface 612 is connected to a network 614, so that processor 602 and computer-readable storage medium 604 are capable of connecting to external elements via network 614. Processor 602 is configured to execute computer program code 606 encoded in computer-readable storage medium 604 in order to cause system 600 to be usable for performing a portion or all of the noted processes and/or methods. In one or more embodiments, processor 602 is a central processing unit (CPU), a multi-processor, a distributed processing system, an application specific integrated circuit (ASIC), and/or a suitable processing unit.

In one or more embodiments, computer-readable storage medium **604** is an electronic, magnetic, optical, electromag-

netic, infrared, and/or a semiconductor system (or apparatus or device). For example, computer-readable storage medium **604** includes a semiconductor or solid-state memory, a magnetic tape, a removable computer diskette, a random access memory (RAM), a read-only memory (ROM), a rigid 5 magnetic disk, and/or an optical disk. In one or more embodiments using optical disks, computer-readable storage medium **604** includes a compact disk-read only memory (CD-ROM), a compact disk-read/write (CD-R/W), and/or a digital video disc (DVD).

In one or more embodiments, storage medium 604 stores computer program code 606 configured to cause system 600 (where such execution represents (at least in part) the EDA tool) to be usable for performing a portion or all of the noted processes and/or methods. In one or more embodiments, 15 storage medium 604 also stores information which facilitates performing a portion or all of the noted processes and/or methods. In one or more embodiments, storage medium 604 stores library 607 of standard cells including such standard cells as disclosed herein.

EDA system **600** includes I/O interface **610**. I/O interface **610** is coupled to external circuitry. In one or more embodiments, I/O interface **610** includes a keyboard, keypad, mouse, trackball, trackpad, touchscreen, and/or cursor direction keys for communicating information and commands to 25 processor **602**.